# Pierre Auger Observatory

# Surface Detector Electronics Upgrade AIT- AIV Plan

Abstract:

This document defines the Assembly, Integration and Test/Verification Plan for the SDEU. It develops the objectives, sequences and resources at system level.

| Document written by | : P. Stassi             | Agreed by:         | Tiina Suomijärvi |

|---------------------|-------------------------|--------------------|------------------|

|                     | Project System engineer |                    | Task Leader      |

| Date:               | 28 April 2017           | Date:              | 28 April 2017    |

| Local Reference:    | ATRIUM-4404             | Project Reference: | WP10-LPSC-111    |

# **Table of Content**

| 1. | Intro                                                                                                                                                              | oduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                   |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | 1.1                                                                                                                                                                | Purpose and scope                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5                                                                                                                                                                 |

|    | 1.2                                                                                                                                                                | Documents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5                                                                                                                                                                 |

|    | 1.2.1                                                                                                                                                              | 1 Reference Documents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5                                                                                                                                                                 |

| 2. | obje                                                                                                                                                               | ctives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6                                                                                                                                                                 |

| 3. | Mod                                                                                                                                                                | lels phylosophy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6                                                                                                                                                                 |

|    | 3.1                                                                                                                                                                | Prototype Boards (PrtB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 6                                                                                                                                                                 |

|    | 3.2.                                                                                                                                                               | Pre-production Boards (PpB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 6                                                                                                                                                                 |

|    | 3.3.                                                                                                                                                               | Production Boards (PB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6                                                                                                                                                                 |

| 4. |                                                                                                                                                                    | ufacturing flow charts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                   |

| 4  | 4.1                                                                                                                                                                | Prototype Boards                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 7                                                                                                                                                                 |

| 4  | 4.2                                                                                                                                                                | Pre-production Boards                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 7                                                                                                                                                                 |

| 4  | 4.3                                                                                                                                                                | Production Boards                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                   |

| 5. | Test                                                                                                                                                               | Tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 9                                                                                                                                                                 |

| 4  | 5.1                                                                                                                                                                | Tank Simulator (TS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                   |

|    | 5.1.1                                                                                                                                                              | 1 Tank Simulator Description (RD6)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 9                                                                                                                                                                 |

| 4  | 5.2                                                                                                                                                                | Basic Test Equipment (BTE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                   |

| 4  | 5.3                                                                                                                                                                | Test PMT Equipment (TPE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                   |

| 4  | 5.4                                                                                                                                                                | Engineering Array (EA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                   |

| 6. |                                                                                                                                                                    | embly Integration and Verification flow charts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                   |

| (  |                                                                                                                                                                    | Prototype Boards                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                   |

| (  |                                                                                                                                                                    | Pre-production Boards                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                   |

|    |                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                   |

| (  |                                                                                                                                                                    | Production Boards Erreur ! Sig                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                   |

| 7. | Test                                                                                                                                                               | s and Verification list                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                   |

| 7. | Tests<br>7.1                                                                                                                                                       | s and Verification list                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 17<br>17                                                                                                                                                          |

| 7. | Tests<br>7.1<br>7.2                                                                                                                                                | s and Verification list<br>Mechanical verification<br>Thermal verification and ageing                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                   |

| 7. | Tests<br>7.1<br>7.2<br>7.3                                                                                                                                         | s and Verification list<br>Mechanical verification<br>Thermal verification and ageing<br>EMC                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                   |

| 7. | Tests<br>7.1<br>7.2<br>7.3                                                                                                                                         | s and Verification list<br>Mechanical verification<br>Thermal verification and ageing<br>EMC<br>Electrical Functional verification                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                   |

| 7. | Tests<br>7.1<br>7.2<br>7.3                                                                                                                                         | as and Verification list<br>Mechanical verification<br>Thermal verification and ageing<br>EMC<br>Electrical Functional verification                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                   |

| 7. | Tests<br>7.1<br>7.2<br>7.3<br>7.4                                                                                                                                  | as and Verification list<br>Mechanical verification<br>Thermal verification and ageing<br>EMC<br>Electrical Functional verification<br>Requirements Verification Matrix<br>Basic Test definition                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                   |

| 7. | Tests<br>7.1<br>7.2<br>7.3<br>7.4<br>7.4.1                                                                                                                         | as and Verification list<br>Mechanical verification<br>Thermal verification and ageing<br>EMC<br>Electrical Functional verification<br>1 Requirements Verification Matrix<br>2 Basic Test definition<br>3 Full Functional test definition                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                   |

| 7. | Tests<br>7.1<br>7.2<br>7.3<br>7.4<br>7.4.1<br>7.4.2                                                                                                                | as and Verification list<br>Mechanical verification<br>Thermal verification and ageing<br>EMC<br>Electrical Functional verification<br>1 Requirements Verification Matrix<br>2 Basic Test definition<br>3 Full Functional test definition<br>4 End to End test definition                                                                                                                                                                                                                                                                                       |                                                                                                                                                                   |

| 7. | Tests<br>7.1<br>7.2<br>7.3<br>7.4<br>7.4.1<br>7.4.2<br>7.4.3<br>7.4.4<br>7.4.4<br>7.4.5                                                                            | s and Verification list<br>Mechanical verification<br>Thermal verification and ageing<br>EMC<br>Electrical Functional verification<br>Requirements Verification Matrix<br>Basic Test definition<br>Full Functional test definition<br>Electrical Functional test definition<br>Requirements verification by testing                                                                                                                                                                                                                                             |                                                                                                                                                                   |

| 7. | Tests<br>7.1<br>7.2<br>7.3<br>7.4<br>7.4.1<br>7.4.2<br>7.4.3<br>7.4.4<br>7.4.5                                                                                     | <ul> <li>and Verification list</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                   |

| 7. | Tests<br>7.1<br>7.2<br>7.3<br>7.4<br>7.4.1<br>7.4.2<br>7.4.3<br>7.4.4<br>7.4.4<br>7.4.5                                                                            | <ul> <li>and Verification list</li> <li>Mechanical verification</li> <li>Thermal verification and ageing</li> <li>EMC</li> <li>Electrical Functional verification</li> <li>Requirements Verification Matrix</li> <li>Basic Test definition</li> <li>Full Functional test definition</li> <li>Full Functional test definition</li> <li>Requirements verification by testing</li> <li>Engineering Array verification</li> <li>Set Up Verification</li> </ul>                                                                                                      |                                                                                                                                                                   |

| 7. | Tests<br>7.1<br>7.2<br>7.3<br>7.4<br>7.4.1<br>7.4.2<br>7.4.3<br>7.4.4<br>7.4.5                                                                                     | <ul> <li>and Verification list</li> <li>Mechanical verification</li> <li>Thermal verification and ageing</li> <li>EMC</li> <li>Electrical Functional verification</li> <li>Requirements Verification Matrix</li> <li>Basic Test definition</li> <li>Full Functional test definition</li> <li>Full Functional test definition</li> <li>End to End test definition</li> <li>Requirements verification by testing</li> <li>Engineering Array verification</li> <li>Set Up Verification</li> <li>Trigger Verification</li> </ul>                                    | $\begin{array}{c} 17\\ 17\\ 17\\ 17\\ 18\\ 20\\ 20\\ 20\\ 24\\ 25\\ 25\\ 25\\ 25\\ 25\\ 27\\ 30\\ 30\\ 30\\ 30\\ 30\\ 30\\ \end{array}$                           |

| 7. | Tests<br>7.1<br>7.2<br>7.3<br>7.4<br>7.4.1<br>7.4.2<br>7.4.3<br>7.4.4<br>7.4.5<br>7.5<br>7.5.1                                                                     | s and Verification list<br>Mechanical verification<br>Thermal verification and ageing<br>EMC<br>Electrical Functional verification Matrix<br>Basic Test definition<br>Full Functional test definition<br>Full Functional test definition<br>Full Functional test definition<br>Full Functional test definition<br>Sequirements verification by testing<br>Engineering Array verification<br>Trigger Verification<br>Timing Verification                                                                                                                         | $\begin{array}{c} 17\\ 17\\ 17\\ 17\\ 18\\ 20\\ 20\\ 20\\ 20\\ 24\\ 25\\ 25\\ 25\\ 25\\ 25\\ 27\\ 30\\ 30\\ 30\\ 30\\ 30\\ 30\\ 30\\ 30\\ 30\\ 30$                |

| 7. | Tests<br>7.1<br>7.2<br>7.3<br>7.4<br>7.4.1<br>7.4.2<br>7.4.3<br>7.4.4<br>7.4.5<br>7.5<br>7.5.1<br>7.5.2                                                            | <ul> <li>and Verification list</li> <li>Mechanical verification</li> <li>Thermal verification and ageing</li> <li>EMC</li> <li>Electrical Functional verification</li> <li>Requirements Verification Matrix</li> <li>Basic Test definition</li> <li>Full Functional test definition</li> <li>Full Functional test definition</li> <li>Engineering Array verification</li> <li>Set Up Verification</li> <li>Trigger Verification</li> <li>Timing Verification with muons</li> </ul>                                                                              | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                              |

| 7. | Tests<br>7.1<br>7.2<br>7.3<br>7.4<br>7.4.1<br>7.4.2<br>7.4.3<br>7.4.4<br>7.4.5<br>7.5<br>7.5.1<br>7.5.2<br>7.5.3                                                   | <ul> <li>and Verification list</li> <li>Mechanical verification</li> <li>Thermal verification and ageing</li> <li>EMC</li> <li>Electrical Functional verification</li> <li>Requirements Verification Matrix</li> <li>Basic Test definition</li> <li>Full Functional test definition</li> <li>Full Functional test definition</li> <li>Engineering Array verification</li> <li>Set Up Verification</li> <li>Trigger Verification</li> <li>Timing Verification with muons</li> <li>Large PMTs, calibration with LED</li> </ul>                                    | $\begin{array}{c} 17\\ 17\\ 17\\ 17\\ 18\\ 20\\ 20\\ 20\\ 24\\ 25\\ 25\\ 25\\ 25\\ 25\\ 25\\ 27\\ 30\\ 30\\ 30\\ 30\\ 30\\ 30\\ 30\\ 30\\ 30\\ 30$                |

| 7. | Test:<br>7.1<br>7.2<br>7.3<br>7.4<br>7.4.1<br>7.4.2<br>7.4.3<br>7.4.4<br>7.4.5<br>7.5.1<br>7.5.2<br>7.5.3<br>7.5.4<br>7.5.5<br>7.5.6                               | s and Verification list<br>Mechanical verification<br>Thermal verification and ageing<br>EMC<br>Electrical Functional verification<br>1 Requirements Verification Matrix.<br>2 Basic Test definition<br>3 Full Functional test definition<br>4 End to End test definition<br>5 Requirements verification by testing<br>Engineering Array verification<br>1 Set Up Verification<br>2 Trigger Verification<br>3 Timing Verification<br>4 Large PMTs, calibration with muons<br>5 Large PMTs, calibration with LED<br>6 Performances comparison                    | $\begin{array}{c} 17\\ 17\\ 17\\ 17\\ 17\\ 18\\ 20\\ 20\\ 20\\ 20\\ 24\\ 25\\ 25\\ 25\\ 25\\ 25\\ 25\\ 25\\ 27\\ 30\\ 30\\ 30\\ 30\\ 30\\ 30\\ 30\\ 30\\ 30\\ 30$ |

| 7. | Test:<br>7.1<br>7.2<br>7.3<br>7.4<br>7.4.1<br>7.4.2<br>7.4.3<br>7.4.4<br>7.4.5<br>7.5.1<br>7.5.2<br>7.5.3<br>7.5.4<br>7.5.5<br>7.5.6<br>7.5.6<br>7.5.6             | s and Verification list<br>Mechanical verification.<br>Thermal verification and ageing.<br>EMC.<br>Electrical Functional verification Matrix.<br>2 Basic Test definition.<br>3 Full Functional test definition<br>4 End to End test definition<br>5 Requirements verification by testing.<br>Engineering Array verification<br>1 Set Up Verification<br>2 Trigger Verification<br>3 Timing Verification<br>4 Large PMTs, calibration with muons<br>5 Large PMTs, calibration with LED<br>6 Performances comparison                                              | $\begin{array}{c} 17\\ 17\\ 17\\ 17\\ 17\\ 18\\ 20\\ 20\\ 20\\ 20\\ 24\\ 25\\ 25\\ 25\\ 25\\ 25\\ 25\\ 25\\ 27\\ 30\\ 30\\ 30\\ 30\\ 30\\ 30\\ 30\\ 30\\ 30\\ 30$ |

| 7. | Test:<br>7.1<br>7.2<br>7.3<br>7.4<br>7.4.1<br>7.4.2<br>7.4.3<br>7.4.4<br>7.4.5<br>7.5<br>7.5.1<br>7.5.2<br>7.5.3<br>7.5.4<br>7.5.5<br>7.5.6<br>7.5.6<br>7.5.6      | s and Verification list<br>Mechanical verification<br>Thermal verification and ageing<br>EMC<br>Electrical Functional verification Matrix<br>2 Basic Test definition<br>3 Full Functional test definition<br>4 End to End test definition<br>5 Requirements verification by testing<br>Engineering Array verification<br>1 Set Up Verification<br>2 Trigger Verification<br>3 Timing Verification<br>4 Large PMTs, calibration with muons<br>5 Large PMTs, calibration with LED<br>6 Performances comparison<br>Models Verification Matrix<br>Quality Assurance | $\begin{array}{c} 17\\ 17\\ 17\\ 17\\ 17\\ 18\\ 20\\ 20\\ 20\\ 20\\ 24\\ 25\\ 25\\ 25\\ 25\\ 25\\ 25\\ 27\\ 30\\ 30\\ 30\\ 30\\ 30\\ 30\\ 30\\ 30\\ 30\\ 30$      |

| 7. | Test:<br>7.1<br>7.2<br>7.3<br>7.4<br>7.4.1<br>7.4.2<br>7.4.3<br>7.4.4<br>7.4.5<br>7.5<br>7.5.1<br>7.5.2<br>7.5.3<br>7.5.4<br>7.5.5<br>7.5.6<br>7.5.6<br>7.7<br>ANN | s and Verification list<br>Mechanical verification.<br>Thermal verification and ageing.<br>EMC.<br>Electrical Functional verification Matrix.<br>2 Basic Test definition.<br>3 Full Functional test definition<br>4 End to End test definition<br>5 Requirements verification by testing.<br>Engineering Array verification<br>1 Set Up Verification<br>2 Trigger Verification<br>3 Timing Verification<br>4 Large PMTs, calibration with muons<br>5 Large PMTs, calibration with LED<br>6 Performances comparison                                              | $\begin{array}{c} 17\\ 17\\ 17\\ 17\\ 17\\ 18\\ 20\\ 20\\ 20\\ 20\\ 24\\ 25\\ 25\\ 25\\ 25\\ 25\\ 25\\ 27\\ 30\\ 30\\ 30\\ 30\\ 30\\ 30\\ 30\\ 30\\ 30\\ 30$      |

# ACRONYMS

| AD         | Applicable Document                                  |

|------------|------------------------------------------------------|

| ADC        | Analog to Digital Converter                          |

| AIT        | Assembly, Integration and Tests                      |

| AIV        | Assembly, Integration and Verification               |

| BGA        | Ball Grid Array                                      |

| BTE        | Basic Test Equipment                                 |

| CDAS       | Central Data Acquisition System                      |

| CPU        | Central Processing Unit                              |

| CR         | Configurational Requirement                          |

| DAC        | Digital to Analog Converter                          |

| DC         | Direct Current                                       |

| DVM        | Digital VoltMeter                                    |

| EA         | Engineering Array                                    |

| EMC        | Electro-Magnetic Compatibility                       |

| ESD        | Electro-Static Discharge                             |

| ESS        | Environmental Stress Screening                       |

| ER         | Environmental Requirement                            |

| FADC       | Flash ADC                                            |

| FDIR       | Failure Detection, Isolation and Recovery            |

|            | Failure Mode, Effects and Criticality Analysis       |

| FMEA       | Failure Mode, Effects Analysis                       |

| FPGA       | Filed Programmable Gate Array                        |

| FR         | Functional Requirements                              |

| GPS        | Global Positioning System                            |

| HASS       | Highly Accelerated Stress Screening                  |

| HSIA       | Hardware Software Interaction Analysis               |

| HV         | High Voltage                                         |

| H/W        | HardWare                                             |

| ICD        | Interfaces Control Document                          |

| IR         | Interface Requirements                               |

| JTAG       | Joint Test Action Group                              |

| LED        | Light Emitting Diode                                 |

| LUD        |                                                      |

|            | Low Voltage Differential Signaling<br>non applicable |

| n/a<br>NCD |                                                      |

| NCR        | Non Conformance Report                               |

| OR         | Operational Requirements                             |

| OTG        | On The Go                                            |

| PB         | Production Board                                     |

| PBS        | Product Breakdown Structure                          |

| PC         | Personal Computer                                    |

| PCB        | printed Circuit Board                                |

| PMT        | PhotoMultiplier Tube                                 |

| PpB        | Pre-production Board                                 |

| PPS        | Pulse Per Second                                     |

| PR         | Physical Requirements                                |

| PrtB       | Prototype Board                                      |

| QR         | Quality Requirements                                 |

| RD         | Reference Document                                   |

| RSS        | Reliability Stress Screening                         |

| SDE        | Surface Detector Electronics                         |

| SPF        | Single Point Failure                                 |

| SPMT       | Small PMT                                            |

| SR         | Support Requirements                                 |

|            |                                                      |

| S/W   | SoftWare                     |

|-------|------------------------------|

| TBC   | To Be Confirmed              |

| TBD   | To Be Defined                |

| TBW   | To Be Written                |

| TC    | Tele-Command                 |

| TM    | TeleMetry                    |

| TPCB  | Tank Power Control Board     |

| TS    | Tank Simulator               |

| UB    | Unified Board                |

| UC    | Upgrade Committee            |

| USB   | Universal Serial Bus         |

| UUB   | Upgraded Unified Board       |

| UHE   | Ultra High Energy            |

| UHECR | Ultra High Energy Cosmic Ray |

| VM    | Verification Matrix          |

- WCT WP Water Cerenkov Tank

- Work Package

# **DOCUMENT CHANGE RECORD**

| Issue | Revision | Issue    | Changes     | Modified Pages Numbers, Change                  |

|-------|----------|----------|-------------|-------------------------------------------------|

|       |          | Date     | Approved by | Explanations and Status                         |

| 11    | А        | 23/03/14 | P. Stassi   | DRAFT                                           |

| 11    | В        | 15/05/14 | P. Stassi   | First release                                   |

| 11    | С        | 05/11/14 | P. Stassi   | Engineering Array verifications added           |

| 11    | D        | 28/11/14 | P. Stassi   | Minor upgrade                                   |

| 11    | Е        | 01/04/15 | P. Stassi   | Flows and test matrix update. Tests definitions |

| 11    | F        | 08/04/15 | P. Stassi   | Updated with WP designers comments              |

| 11    | G        | 15/09/15 | P. Stassi   | M. Kleifges proposal integration, QA added.     |

| 11    | Н        | 17/10/16 | P. Stassi   | Update before Auger prime CDR                   |

| 11    | Ι        | 28/04/17 | P. Stassi   | Update for Test System internal PRR             |

|       |          |          |             |                                                 |

|       |          |          |             |                                                 |

|       |          |          |             |                                                 |

#### 1. INTRODUCTION

#### 1.1 Purpose and scope

This document describes the ways and means:

- To ensure the SDEU assembly and its integration,

- To ensure its verification,

- To test and/or measure its performances.

It will:

- Present the general objectives of the SDEU AIT-AIV,

- Give the verification philosophy,

- Identify and describe the AIT-AIV tasks at system and sub-system level,

#### 1.2 Documents

#### 1.2.1 Reference Documents

- RD1 SDEU Specifications, WP10LPSC03.

- RD2 SDEU Development Plan, WP10LPSC02.

- RD3 SDEU Electrical Interfaces Control Document, WP10LPSC05.

- RD4 AUGER GAP NOTE, GAP-2002-002.

- RD5 IEC 61004, Electromagnetic compatibility (EMC) Part 4-2: Testing and measurement techniques Electrostatic discharge immunity test.

- RD6 The UUB Test System, P. Buchholz and Al, Siegen University, Jan. 28<sup>th</sup> 2015

- RD7 Design, Fabrication & Testing of the Auger Surface Detector Front End Electronics Board, Daw Don Cheam, MTU 2004.

- RD8 PAO Project Management Plan 2013-05

- RD9 SDE Quality Management Plan SDE\_QMP-2002-04

## 2. OBJECTIVES

- Verification by means of testing of the SDEU system with respect to the specification, including operational procedures;

- Establish an integration sequence for the units;

- Identification of test activities at unit level;

- Identify the procedures for the various tests.

#### 3. MODELS PHYLOSOPHY

#### 3.1 Prototype Boards (PrtB)

This model is needed to test and validate the design of the SDEU. 5 plus 20 units of PrtB will be realized and tested at various plants. 10 units will be shipped to PAO site to be tested on the engineering array.

#### 3.2 Pre-production Boards (PpB)

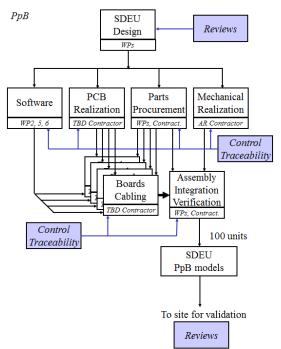

The PpB model is needed for manufacturer qualification. 100 units are foreseen for this purpose. Four productions sites are foreseen then the numbers of PpB will be spread among the production sites (~ 33 units per site).

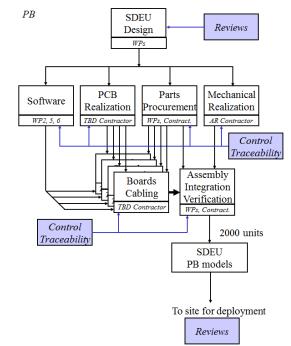

#### 3.3 Production Boards (PB)

2000 units of the PB model will be manufactured on four production sites, equally distributed. The PCB will be fabricated in one site only (TBC).

# 4. MANUFACTURING FLOW CHARTS

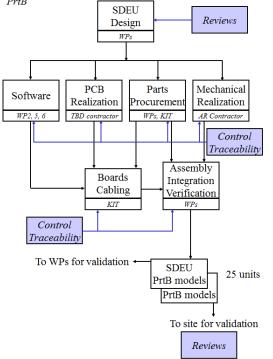

# 4.1 Prototype Boards PrtB

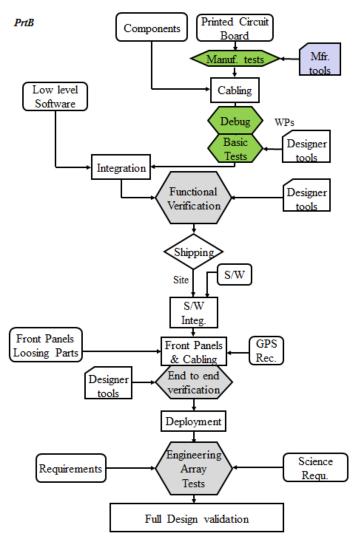

Figure 4.1a: Prototype boards manufacturing flow chart

4.2 Pre-production Boards

Figure 4.2a: Pre-production boards manufacturing flow chart

## 4.3 Production Boards

Figure 4.3a: Production boards manufacturing flow chart

## 5. TEST TOOLS

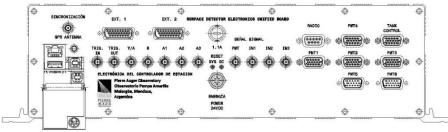

#### 5.1 Tank Simulator or Test System (TS)

To verify all the requirements of the SDEU and also to be able to operate it at the various test plant, a "Tank Simulator" will be built, not only able to generate or receive and monitor signals to and from the UUB under test, but also able to have the basic behavior of the real tank and devices around.

Additionally, this kind of simulator can be easily reproduced and spread through the different partners, allowing sharing test and validation activities.

The "Tank Simulator" should be able to be used for the specification validation of the UUB but also for the functional verification, fabrication and production validation and reception, maintenance and failure detection and recovery.

#### 5.1.1 Tank Simulator Description (RD6)

#### 5.1.1.1 Simulation interfaces

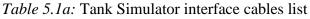

Interfaces reproduced by the TS come as a set of 26 cables connections:

| Name         | Description (SDEU wise)                   |

|--------------|-------------------------------------------|

| POWER 24VDC  | Power input                               |

| EXT1         | Digital LVDS I/O port                     |

| EXT2         | Digital LVDS I/O port                     |

| ETH          | Ethernet port                             |

| USB OTG      | USB OTG port                              |

| USB SYS      | USB system port                           |

| USB SC       | USB slow control port                     |

| TRIG. IN     | Trigger digital input                     |

| TRIG. OUT    | Trigger digital output                    |

| Y/A          | LED analog signal output                  |

| R            | LED analog signal output                  |

| IN1          | SSD detector analog input                 |

| IN2          | Other detector analog input               |

| IN3          | Other detector analog input               |

| PMT          | Small PMT analog input                    |

| A1           | PMT analog input                          |

| A2           | PMT analog input                          |

| A3           | PMT analog input                          |

| RADIO        | Radio serial port                         |

| TANK CONTROL | Tank slow control port (analog & digital) |

| PMT1         | PMT slow control port (analog)            |

| PMT2         | PMT slow control port (analog)            |

| PMT3         | PMT slow control port (analog)            |

| PMT4         | Small PMT slow control port (analog)      |

| PMT5         | SSD PMT slow control port (analog)        |

| PMT6         | Other PMT slow control port (analog)      |

Figure 5.1b: SDEU front panel TO BE UPDATED

Mechanical, electrical aspects and content definition of these interfaces are summarized in RD1 and RD3.

#### 5.1.1.2 Interaction schemes

The Tank Simulator is not intended for any mechanical test of its interfaces.

Electrical interactions parameters (load, impedance...) shall comply with SDEU requirements (RD1, RD3) on all interfaces.

GPS antenna signal will not be considered and simulated.

#### 5.1.1.3 On Analog interfaces

The TS will provide realistic anode PMT signals, adjustable in amplitude and time, with all possible coincidence combination, in order to be able to test all the trigger configurations.

#### 5.1.1.4 On power supplies interface

The TS will provide 24 Volts power supply, adjustable between 18 and 32 Volts (TBC), able to reproduce the real voltage variation due to day and/or seasonal sun light variations. A set of degraded interaction and fault condition schemes will be considered and implemented (TBD).

#### 5.1.1.5 On communication interfaces

The TS will be able to communicate on each defined port of the UUB. A set of degraded interaction and fault condition schemes will be considered and implemented.

#### 5.1.1.6 On Slow-Control interfaces

The TS will be able to emulate all sensors answer of the real tanks and monitor all PMT high voltage command send by the UUB. A set of degraded interaction and fault condition schemes will be considered and implemented.

#### 5.1.1.7 On LED

The TS will be able to monitor the signal from the LED controller send by the UUB and emulate PMT response on generated anode signal, accordingly to the LED signal parameters (time, amplitude). A set of degraded interaction and fault condition schemes will be considered and implemented.

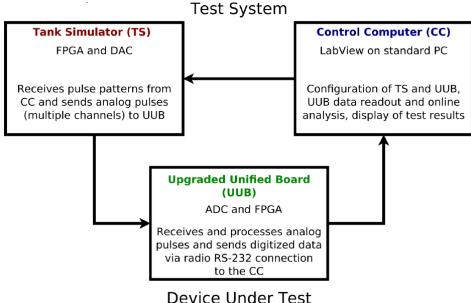

#### 5.1.1.8 Setup description

The local TS setup is composed with the following items:

Device Under Test

Figure 5.1c: Tank simulator setup diagram

5.1.1.9 Application description (TBC)

The Tank Simulator applicative software allows user to:

- Generate anode PMT signals, eventually reconstructed from real signal recorded, for the 3 regular PMTs, the Small PMT and all other additional PMTs foreseen for the muon detectors upgrade.

- Generate power supply including optionally the daily and seasonal variations recorded from the real data.

- Generate environmental sensors signal recorded from the real data.

- Receive and monitor all slow control signal issued, used for PMT control and monitoring.

- Emulate all signal and protocol on digital I/O line, including, JTAG and trigger ports.

- Emulate the communication protocol used for the COMMS radio system.

- Emulate LED responses to signal emitted by UUB.

Additionally, the Tank Simulator should monitor and evaluate (automatically or not) all signal incoming from the UUB under test, to perform a kind of failure detection

Moreover, the Tank simulator should be able to emulate the basic behavior of a real tank, for example, an increase of the command voltage of the HV bias on a PMT should result to a realistic increase of the anode pulse signal amplitude.

Additionally, to facilitate software adjustment and modification by user people, the TS applicative software interface shall be developed in graphical programming language, LabVIEW<sup>®</sup>.

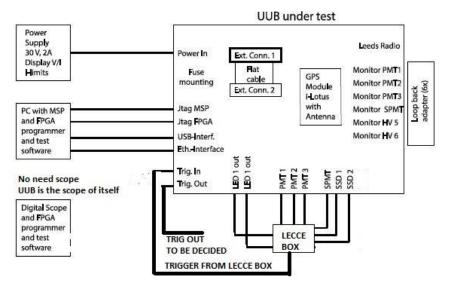

# 5.2 Basic Test Equipment (BTE)

Beside the TS equipment, a Basic Test Equipment set up is defined and described below. This equipment can be used as an alternative of the TS to perform the basic test procedure for the production and pre-production models (TBC).

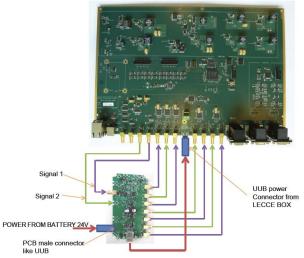

Figure 5.2a: BTE setup diagram

The Basic Test Equipment consists of:

- a power supply (30V, 2A) with current limitation and display for current and voltage

- a computer (under Linux) with test software and programmer for microcontroller and

- FPGA; USB, Ethernet and JTAG cables to connect the PC with the UUB

- a fast digital oscilloscope ( < 2chn., GHz sampling)

- an active splitter (Lecce Box) to fed the signals from the LED pulser into the PMT inputs; Alternatively a signal generator can be used.

- 6 test adapters (emulating feedback loops) for the HV monitoring outputs

- a special 26-pol flat cable to interconnect the external connectors 1/2 (for feedback loop)

Figure 5.2b: Lecce Box usage

# 5.3 Test PMT Equipment (TPE)

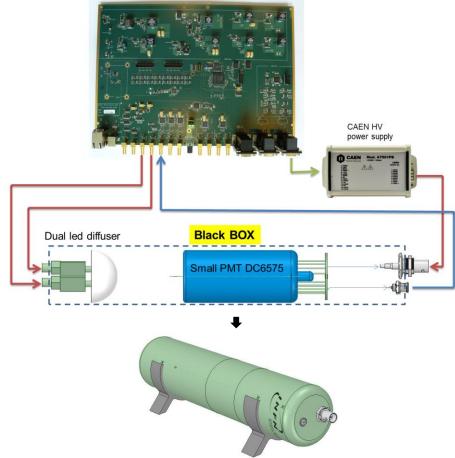

Associated with other measurement equipment, the Test PMT Equipment generates real PMT signal toward the analog inputs of the UUB, triggered by the onboard LED controller. The PMT polarization high voltage is provided from the UUB PMT slow control connector, through a dedicated commercial HV module (CAEN):

Figure 5.3a: TPE setup diagram

This configuration, used to pre-prototypes and prototypes models, allows the verification and the measurement of the analog "Front End" parameters:

- Digitalization

- Analog and digital dynamic ranges

- Linearity

- Acquisition rate

Moreover, the TPE could also being used for some trigger configuration tests and PMT slow control algorithm.

## 5.4 Engineering Array (EA)

A small area, including a set of an array of 7 Water Cerenkov Tanks (WCT) equipped with new SSD setup, dedicated for test and validation will be setup in a place of the SD area (see map below).

These Engineering Array WCTs will be equipped with the power supply system, and the whole communication setup. Large and small PMTs and LED flasher will be also installed.

The EA purpose is to complete the validation of the design and to verify the performances of the SD equipped with SDD and UUB, in situ.

Figure 5.4a: Engineering Array location

Figure 5.4b: Engineering Array Setup

# 6. ASSEMBLY INTEGRATION AND VERIFICATION FLOW CHARTS

# 6.1 Prototype Boards

Figure 6.1a: Prototype boards AIV flow chart

Procurement Integration, Shipment and Deployment activities Testing and Verification activities Testing tools

The design will be validated on the prototype boards by the WP designers and the results of the engineering array tests on site.

ESD (EMC) test are also included in the electrical verification process, but only on the prototype model (PrtB).

# 6.2 Pre-production and production Boards

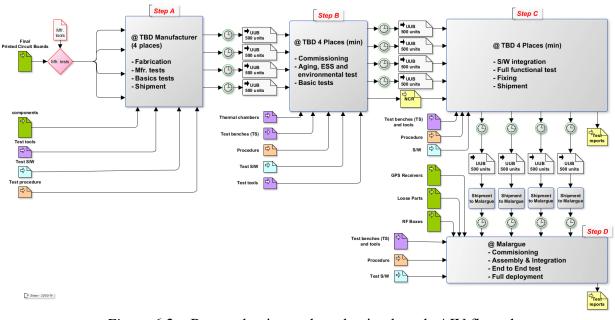

Figure 6.2a: Pre-production and production boards AIV flow chart

The flow is adapted to the 4 productions sites (TBC). The S/W integrated should include a part dedicated to test, activated with on board micro-switches. Four sites at the minimum are foreseen for the ESS and Burning tests.

The validation of the manufacturers' process will occur after the pre-production deployment on site.

The production and test plan can be described in 4 steps (RD2):

- **Step A**, board manufacturing. Several places are foreseen, depending of the contribution policy in the collaboration. However one unique manufacturer (subcontractor) is recommended. Only one manufacturer for the PCBs is foreseen.

- **Step B**, several place are foreseen for the commissioning, ageing and environmental tests. These places are chosen within the institutes of the collaboration.

- **Step C**, several place are foreseen for the S/W integration and full functional tests. These places are chosen within the institutes of the collaboration.

- On institute is responsible for the UUB shipment to the PAO site

- **Step D**. PAO Site, commissioning, integration, end to end tests and deployment.

#### 7 TESTS AND VERIFICATION LIST

#### 7.1 Mechanical verification

The goal of SDEU mechanical verification is essentially focused of the board dimensions, regarding the reused metallic housing and the front panel connector holes, regarding the positions of the implemented connectors on the UUB PCB. These verifications can be realized by review of design.

#### 7.2 Thermal verification and ageing

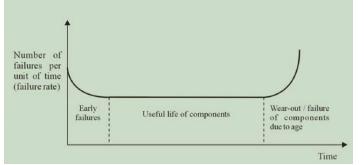

Due to long operational life required, in a difficult environmental stress (daily thermal cycling with a minimum of -15 degrees and a maximum of +55 degrees Celsius) and also to eliminate youth default, we need an environmental stress screening and a Burn-in procedure to enhance the reliability of each UUB.

Components are more likely to fail within the early and late life part of a device, in consequence, the life-time reliability characteristic looks like a 'Bath-Tub'. (RD4).

Figure 7.2a: The 'Bath-Tub' life-time reliability characteristic

Environmental stress screening (ESS), also known as Reliability Stress Screening (RSS), is used in industry both at the design and the production level to minimize failure of equipment in the field.

Design level testing is used to locate inherent faults and weaknesses within a design before full-scale production is undertaken. Production level screening is used to locate faulty components and manufacturing defects that would create equipment failures in the field environment

The ESS of electronic assemblies is used to provide initial thermal ageing of devices before delivery i.e. to accelerate the ageing of an assembly to pass through the initial high-failure period, principally by revealing manufacturing defects.

ESS procedure is only used to provide initial ageing of devices (HASS: Highly Accelerated Stress Screening). The objective is to detect the weakest points.

Process constraints to be used during the environmental stress screening and Burn-in, in order to release a full HASS and to simulate usage in the field:

- The UUB is powered on, and the basic functionality should be performed.

- Failures appearing in hot temperature conditions are different of those appearing in cold temperature conditions. Indeed 80% of failures (physical) occur in cold conditions (contraction effect).

- During the ESS, the power supply voltage should be chosen for the worst conditions.

- Environmental conditions: humidity is between 5 to 100%, sand presence < 300 mg/m<sup>3</sup>, salt fog is moderated.

- Temperature should be reached within 30 minutes but no faster than 10 minutes to avoid thermal shock effects.

- Check of the cold/hot start capability (applying electrical stimulus: powered off during a specified time and powered up at each extreme temperature).

- We need to provide an electrical test before and after ESS and Burn-in, and a full functional test after, using the Tank Simulator.

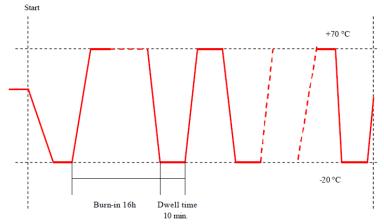

- The feedback of the last years of electronic industry indicates that the use of Burn-in is not as efficient as ESS (The Burn-in submits the boards to hot temperature conditions during a specified time). Using a calibration procedure (see below) we plan to mix an ESS with a Burn-in; First, we begin with a cold cycle, and next a Burn-in session at +70 Deg.C (16 to 40 hours, for ageing), then ESS session (10 cycles from -20 Deg.C to +70 Deg.C.; 6 Deg.C. by minute and 10 minutes extreme steps time)

Figure 7.2b: ESS and Burn-in temperature profile

#### 7.3 EMC

EMC verification will follow the RD5 document, IEC61000, part 4-2, *Testing and measurement techniques - Electrostatic discharge (ESD) immunity test.*

This standard relates to equipment, systems, subsystems and peripherals which may be involved in static electricity discharges owing to environmental and installation conditions, such as low relative humidity, use of low-conductivity (artificial-fiber) carpets, vinyl garments, etc., which may exist in all locations classified in standards relevant to electrical and electronic equipment.

Contact discharge is the preferred test method. Air discharges shall be used where contact discharge cannot be applied. Voltages for each test method are given in Table 7.3a. The voltages shown are different for each method due to the differing methods of test.

Table 7.3b shows the application of the test levels related to environmental (installation) classes.

For air discharge testing, the test shall be applied at all test levels in Table 7.3a up to and including the specified test level. For contact discharge testing, the test shall be

applied at the specified test level only unless otherwise specified by product committees.

|                | Contact discharge |       | Air discharge |  |

|----------------|-------------------|-------|---------------|--|

| Level          | Test voltage      | Level | Test voltage  |  |

| Level          | kV                |       | kV            |  |

| 1              | 2                 | 1     | 2             |  |

| 2              | 4                 | 2     | 4             |  |

| 3              | 6                 | 3     | 8             |  |

| 4              | 8                 | 4     | 15            |  |

| х <sup>а</sup> | Special           | хa    | Special       |  |

a "x" can be any level, above, below or in between the others. The level shall be specified in the dedicated equipment specification. If higher voltages than those shown are specified, special test equipment may be needed.

| Class            | Relative humidity<br>as low as | Antistatic<br>material | Synthetic<br>material | Maximum voltage   |

|------------------|--------------------------------|------------------------|-----------------------|-------------------|

|                  | %                              |                        |                       | kV                |

| 1<br>2<br>3<br>4 | 35<br>10<br>50<br>10           | x<br>x                 | x<br>x                | 2<br>4<br>8<br>15 |

Table 7.3b: Guideline for the selection of the test levels

For the SDEU ESD tests, taking into account the PAO environment, the class 4 and level 4 should be considered.

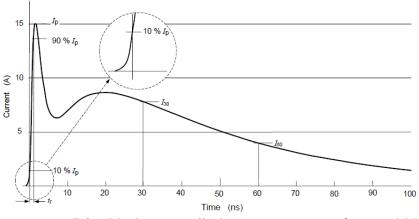

Figure 7.3c: Ideal contact discharge current waveform at 4 kV

#### 7.4 Electrical Functional verification

#### 7.4.1 Requirements Verification Matrix

The method and level for the requirements verifications are described in the following matrix (see RD1 for a description of the requirements):

Four methods are used to verify the requirements:

- **Inspection (I)**. The requirement implementations are verified by a visual inspection of the system and its sub systems.

- **Review of Design (R)**. The requirement implementations are verified by a review of the design documents (schematics, reports, pictures, etc.) of the system and its sub systems.

- **Analysis** (A). The requirement implementations are verify through analysis reports, showing result on mathematical or software models of the sub system concerned.

- **Test (T)**. The requirement implementations are verified through test reports showing results on test procedures applied on the system and its sub systems.

The verifications can be performed at two levels, **System** (S) or **Sub System** (SS) or **Both** (B)

|              | Verification Matrix                                                                                                                                                                                                                                                                                                                                                   |            |        |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------|

| Requirements |                                                                                                                                                                                                                                                                                                                                                                       |            | cation |

| ID           | Text                                                                                                                                                                                                                                                                                                                                                                  | Metho<br>d | Level  |

| FR11         | The UUB shall processes analog anode signals from the three PMTs. A low and high gain signal for each PMT shall be conditioned and digitized.                                                                                                                                                                                                                         | Т          | В      |

| FR12         | The total RMS integrated noise at the ADC input shall not exceed 0.5 LSB.                                                                                                                                                                                                                                                                                             | R          | SS     |

| FR13         | The UUB shall digitize the PMTs anode signals at a sampling frequency of 120 Msp/s with a resolution of 12 bits minimum with the adapted conditioning and gain circuitry.                                                                                                                                                                                             | R          | В      |

| FR14         | Adapted anti-aliasing filters shall be implemented for each PMT signal inputs (60Mhz at -3dB, TBC) (<5% single time bin aliasing noise)                                                                                                                                                                                                                               | Т          | В      |

| FR15         | The UUB shall process analog signals from additional detectors                                                                                                                                                                                                                                                                                                        | R          | SS     |

| FR16         | The high gain/low gain ratio shall be of 32.                                                                                                                                                                                                                                                                                                                          | Т          | SS     |

| FR17         | The UUB shall processes analog anode signals from the fourth small additional PMT ( the purpose is to increase the overall energy dynamic range).                                                                                                                                                                                                                     | R          | SS     |

| FR21         | The trigger/memory circuitry shall evaluate the high-gain output of each PMT every 8.3 ns for interesting trigger patterns (see FR26), store the data in buffer and inform the micro-processor circuitry.                                                                                                                                                             | R          | s      |

| FR22         | The trigger/memory circuitry shall generate a first level trigger based upon hardware analysis of the high gain PMT channel waveforms. The UUB micro-processor software shall imposes additional constraints to generate a level 2 trigger signal.                                                                                                                    | Т          | в      |

| FR23         | The goal of the first level trigger shall be to trigger efficiently on UHE cosmic ray air showers of energy >1019eV, while simultaneously rejecting lower energy showers and minimizing composition dependent trigger biases, within a rate constraint of 100 Hz.                                                                                                     | Т          | в      |

| FR24         | The level 1 trigger shall be designed to be flexible and eventually modifiable in the future                                                                                                                                                                                                                                                                          | R          | SS     |

| FR25         | The level 1 trigger shall start waveforms recording during 19.2 µs                                                                                                                                                                                                                                                                                                    | R          | SS     |

| FR26         | The triggers to be implemented are: etc (see RD1)                                                                                                                                                                                                                                                                                                                     | R-T        | В      |

| FR27         | The level 1 trigger shall provide signal to Time-Tagging circuitry allowing time step of trigger and determination of absolute time of each ADC bin.                                                                                                                                                                                                                  | Т          | s      |

| FR31         | The UUB shall able to time tag each events, using the information given by a commercial GPS unit and a logic circuitry (in FPGA) based on the existing design.                                                                                                                                                                                                        | Т          | В      |

| FR32         | The time tagging unit shall have a resolution of 4 ns or better, stable in temperature better than 5%.                                                                                                                                                                                                                                                                | Т          | В      |

| FR41         | The UUB shall have a micro-processor able to perform the following tasks:<br>- Level 2 Trigger<br>- Data acquisition and event building with double buffering and recording<br>- Calibration process including analog inputs base line monitoring<br>- Data compression to fit the communication flux limit<br>- Communication with the slow control management unit. | R          | S      |

| FR51         | The UUB shall have a slow control unit, allowing measurement and monitoring of at least 64 x 0 to 5 Volts analog input signals coded over 12 bits (can be multiplexed) and 8 logic inputs. Number of channel shall accommodate the designs for additional muon detector.                                                                                              | R          | SS     |

|              | Verification Matrix                                                                                                                                                                                                   | Verifi     |       |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------|

|              | Requirements                                                                                                                                                                                                          |            |       |

| ID           | Text                                                                                                                                                                                                                  | Metho<br>d | Level |

| FR52         | The UUB shall have a slow control unit able to generate at least 8 x 0 to 2.5 Volts analog buffered output                                                                                                            | R          | SS    |

| TKJ2         | signals coded from 12 bits and 8 logic buffered outputs.                                                                                                                                                              | К          | 66    |

| FR53         | The UUB shall have a slow control unit able to monitor internal parameters to perform a failure detection, isolation and recovery (FDIR) process on onboard power supplies and batteries voltage protection over 35 V | Т          | S     |

| 1105         | and under 22 V)                                                                                                                                                                                                       | -          | 5     |

| FR54         | The UUB slow control unit shall be able to manage all existing SDE environmental sensors and additionally,                                                                                                            | Т          | SS    |

| 1101         | a water temperature sensor and an atmospheric pressure sensor.<br>The UUB shall have a light generator unit (LED controller) able to generate two adapted signals with at least                                       | -          | 00    |

| FR61         | amplitude of 20 Volts towards the two foreseen light devices (LED driver). The signal shall be controlled in                                                                                                          | т          | S     |

| 11101        | time with a resolution of 4 ns and shall be synchronized to the time tagging signal (1PPS)                                                                                                                            |            |       |