PIERRE AUGER OBSERVATORY

### Surface Detector Electronics Upgrade Critical Design Review

### WP7 – Calibration and control tools

Luca Latronico <u>luca.latronico@to.infn.it</u>

SDEU CDR - WP7 - IPNO 4-2-2015

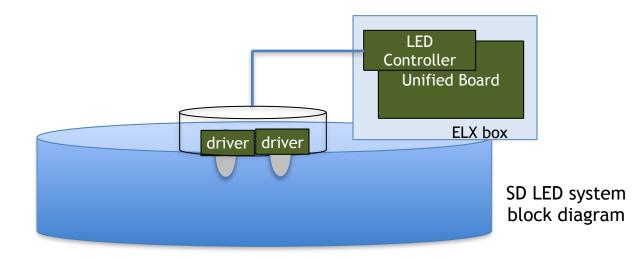

# LED system overview

- Requirements

- Measure PMT linearity over full dynamic range (~20 bits)

- Cross calibrate readout channels

- ANODEx1, ANODEx32, SmallPMT

- Create artificial EAS events on the SD array

- Nota Bene the LED system:

- does NOT perform ALL necessary calibrations for science data acquisition

- supports, does NOT replace, routine calibrations

# **Design concept**

- two LED that can be triggered simultaneously and independently

- for linearity and cross-calibrations

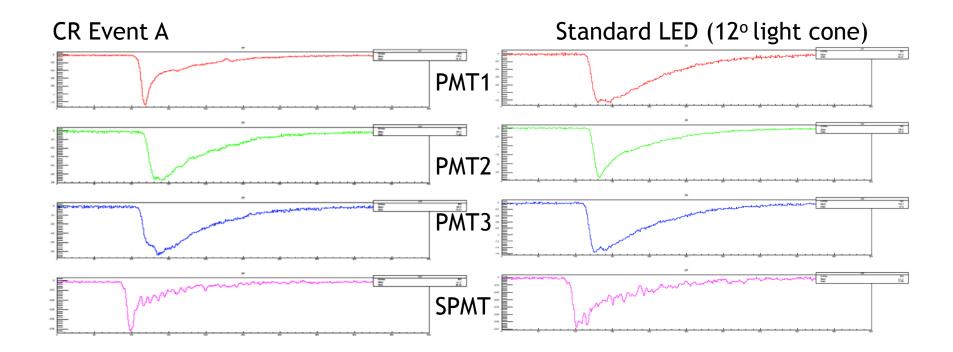

- pulse shape similar to CR and determined by tank

- GPS trigger with arbitrary delay

# **Design implementation**

- Use existing LED on tanks

- flashers, driver, mechanics

- working on ~90% of SD array, missing on InFill

- New LED controller

- Add GPS synchronization with programmable delay

# **Design implementation**

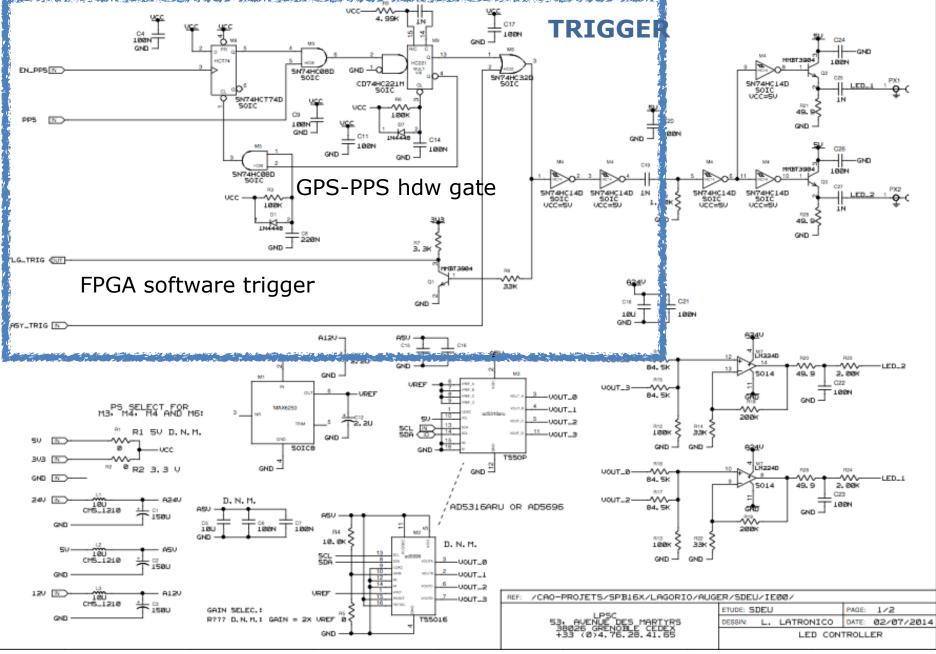

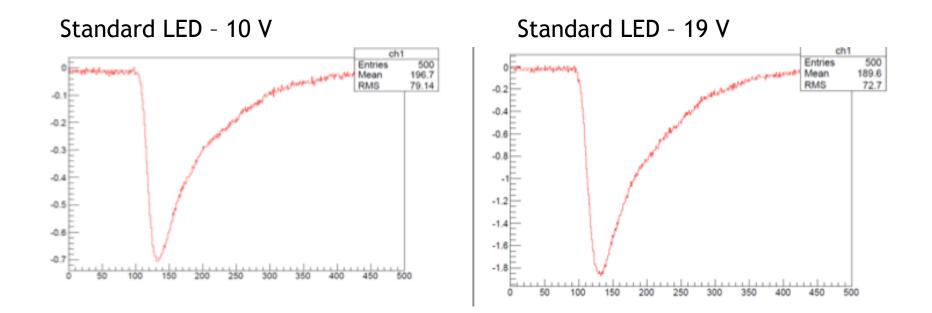

- Increased LED bias

- smallPMT dynamics sampled in the field with 19V

- UUB will provide unregulated DC line, limited to 24V, for further extension

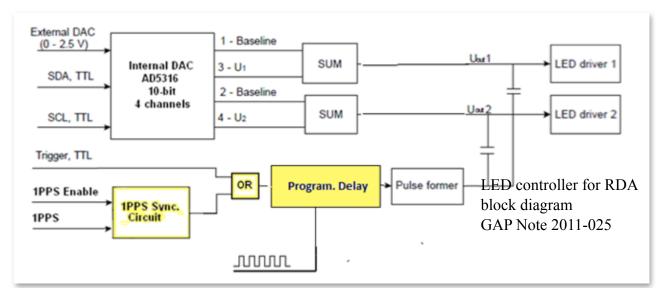

- GPS trigger synchronization

- via a hardware gate around GPS-PPS

- via FPGA timing with arbitrary delay

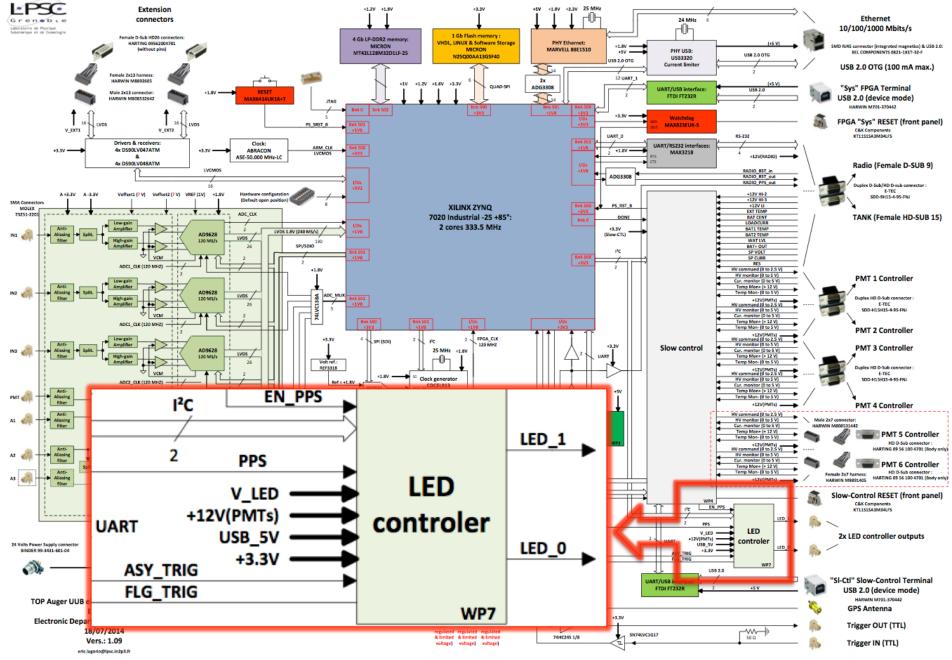

#### Upgraded Unified Board and LED connections Engineering Array Production

## **LED Controller - connections**

| Connection           | Direction | Function                                     |  |  |

|----------------------|-----------|----------------------------------------------|--|--|

| EN_PPS               | INPUT     | Enable PPS signal from Slow<br>Control (WP4) |  |  |

| PPS                  | INPUT     | GPS PPS signal directly from GPS             |  |  |

| ASY_TRG              | INPUT     | software trigger from UUB FPGA               |  |  |

| FLG_TRG              | OUTPUT    | LED trigger flag to UUB FPGA                 |  |  |

| 5V                   |           | For digital circuit                          |  |  |

| 3.3V                 |           | For digital circuit                          |  |  |

| 19-32V (unregulated) |           | Analog bias to LED, limited to 24V           |  |  |

Control through I2C bus via Linux drivers (per WP6 recommendations) SDEU CDR - WP7 - IPNO 4-2-2015

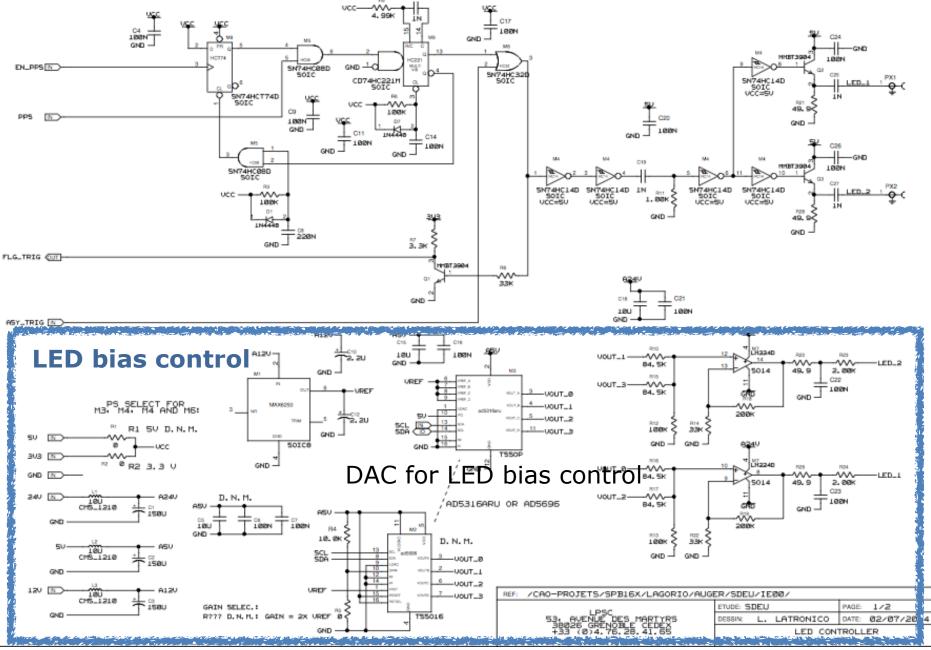

#### **NEW LED Controller (Engineering Array Production)**

SDEU CDR - WP7 - IPNO 4-2-2015

#### **NEW LED Controller (Engineering Array Production)**

SDEU CDR - WP7 - IPNO 4-2-2015

## **Test reports - past examples**

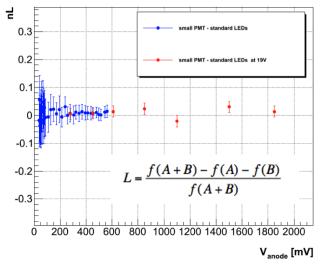

- 1. Non linearity

- does not probe SMPT saturation

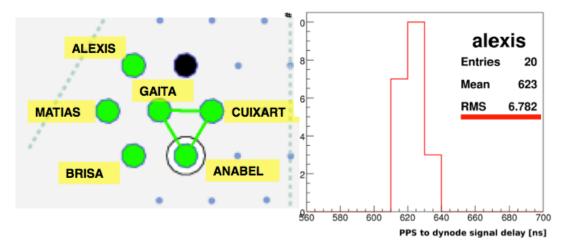

3. Artificial EAS patterns on the array (LED modified controllers for RDA, GAP 2011-25)

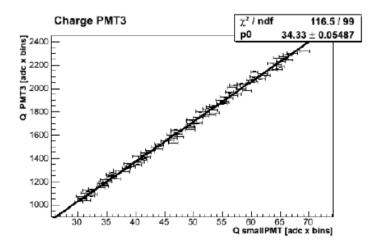

time dispersion of PPS aligned pulses on one tank 2. Inter-range calibration (PMT3-Anode vs SPMT)

# **Test strategy**

- Laboratory Tests for early prototypes

- basic functional tests of the electrical connections

- verify control of the bias DAC

- run full linearity tests without PMTs

- develop and tune test protocol

- Field tests (Engineering Array)

- functional tests

- GPS timing

- linearity and cross-calibrations

# Conclusions

- Status

- system design complete and flown down to WP5

- final layout to be validated

- ready for pre-production

- References

- SDE Upgrade Plan

- SDE Upgrade Specifications

- GAP 2011-25

SDEU CDR - WP7 - IPNO 4-2-2015

# **Small PMT linearity**

Higher input voltage can generate more light, similar signal shape

# Signal shape

## WP7 WBS

| WBS         | Activity                                             | Quant | Base<br>Unit | Est<br>Code | Contin gency | Cost / Unit | Total Cost<br>with Cont. | Total<br>WP cost | FTE-Me |

|-------------|------------------------------------------------------|-------|--------------|-------------|--------------|-------------|--------------------------|------------------|--------|

| 1.7         | Calibration and control tools - WP7                  |       |              |             |              |             |                          | 136987.5         | 96.0   |

| 1.7.1       | Calibration and control design H/W and S/W           |       | hours        | EE          | 30%          | 35          | 0                        | 22522.5          |        |

| 1.7.1.1     | Prototype Board                                      | 2     | each         |             |              | 4550        | 9100                     |                  |        |

| 1.7.1.1.1   | Design Prototype                                     | 60    | hours        | EE          | 30%          | 35          | 2730                     |                  |        |

| 1.7.1.1.2   | CAD Layout                                           | 60    | hours        | EE          | 30%          | 35          | 2730                     |                  |        |

| 1.7.1.1.3   | Procure Parts                                        | 2     | each         | EE          | 30%          |             | 0                        | 1                |        |

| 1.7.1.1.4   | Prototype PCB's                                      | 2     | each         | EE          | 30%          |             | 0                        |                  |        |

| 1.7.1.1.5   | Assemble prototype PCB's                             | 80    | hours        | EE          | 30%          | 35          | 3640                     |                  |        |

| 1.7.1.2     | S/W integration                                      | 80    | hours        | EE          | 30%          | 35          | 3640                     | 1                |        |

| 1.7.1.3     | Functional testing of prototype                      | 80    | hours        | EE          | 30%          | 35          | 3640                     |                  |        |

| 1.7.1.4     | Test on UUB Prototypes (E. Array) and pre-production | 5     | days         | EE          | 30%          | 35          | 227.5                    |                  |        |

| 1.7.1.5     | Integration on UUB design                            | 80    | hours        | EE          | 30%          | 35          | 3640                     |                  |        |

| 1.7.1.6     | Reports and documentation                            | 50    | hours        | EE          | 30%          | 35          | 2275                     |                  |        |

|             |                                                      |       |              |             |              |             |                          |                  |        |

| 1.7.2       | Light generator design                               | 80    | hours        | EE          | 30%          | 35          | 3640                     | 114465           |        |

| 1.7.2.1     | Prototype design                                     | 2     | each         |             |              | 1365        | 2730                     |                  |        |

| 1.7.2.1.1   | Procure Parts                                        | 2     | each         | EE          | 30%          |             | 0                        |                  |        |

| 1.7.2.1.2   | Fabricate prototype                                  | 40    | hours        | EE          | 30%          | 35          | 1820                     |                  |        |

| 1.7.2.1.3   | Assemble prototype                                   | 20    | hours        | EE          | 30%          | 35          | 910                      |                  |        |

| 1.7.2.2     | Functional testing of prototype                      | 40.0  | hours        | EE          | 30%          | 35          | 1820                     | 1                |        |

| 1.7.2.3     | Production                                           | 2000  | each         |             |              | 14.56       | 29120                    |                  |        |

| 1.7.2.3.1   | Procure Parts for production                         | 2050  | each         | EE          | 30%          |             | 0                        |                  |        |

| 1.7.2.3.2   | Fabricate production                                 | 320.0 | hours        | EE          | 30%          | 35          | 14560                    |                  |        |

| 1.7.2.3.3   | Assemble production                                  | 320.0 | hours        | EE          | 30%          | 35          | 14560                    |                  |        |

| 1.7.2.4     | Functional testing and validation of production      | 160.0 | hours        | EE          | 30%          | 35          | 7280                     |                  |        |

| 1.7.2.5     | Onsite shipment                                      | 2000  | each         | EE          | 30%          | 5           | 13000                    |                  |        |

| 1.7.2.6     | Receive/Inspect                                      | 80.0  | hours        | EE          | 30%          | 35          | 3640                     | 1                |        |

| 1.7.2.7     | Onsite integration                                   | 125   | days         | EE          | 30%          | 280         | 45500                    | 1                |        |

| 1.7.2.8     | Validation                                           | 160   | hours        | EE          | 30%          | 35          | 7280                     | 1                |        |

|             | Table 1 Table 2 Feuil +                              |       | I .          |             | C            |             |                          |                  |        |

| Normal View | Ready                                                |       | 1            | Sum=0       |              | ⊖ SCRL ⊖ C  | APS 🕤 NUM                |                  |        |