## WP1- Technical Design Report 2015

R. Assiro, P. Creti, G. Marsella

# Outline

- Specific requirements

- Design concept and solution selected

- Prototype test board design

- Test report and results on prototype

- Design Status

# Specific requirements

The wp1 is in charge to design the analog PMTs processing signal. The new specific requirements are:

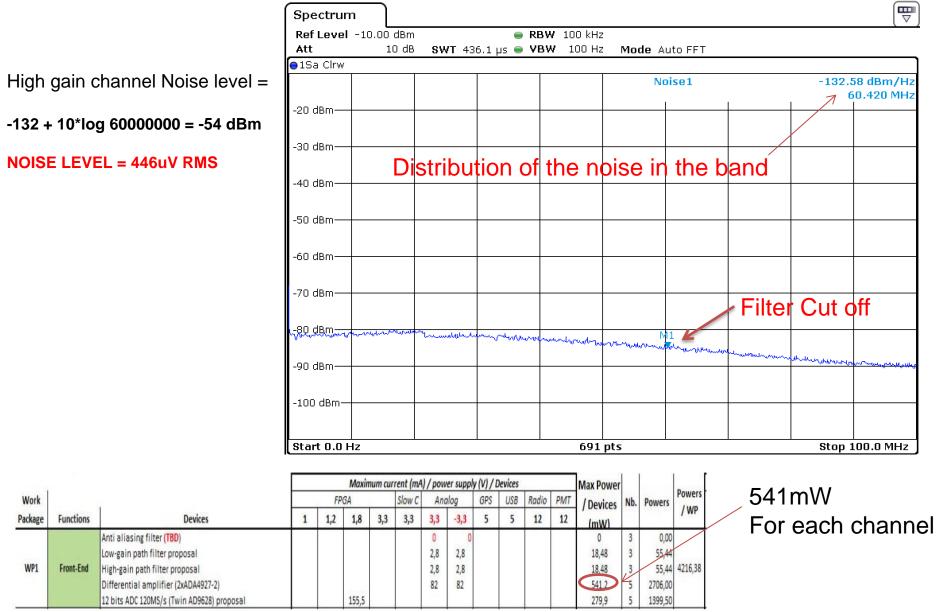

- 5x2 differential channels, low noise (0.5 LSB < 250  $\mu V$ ), 12 bit, and 120 MHz ADC converter

- Power < 0.5 Watt/channel

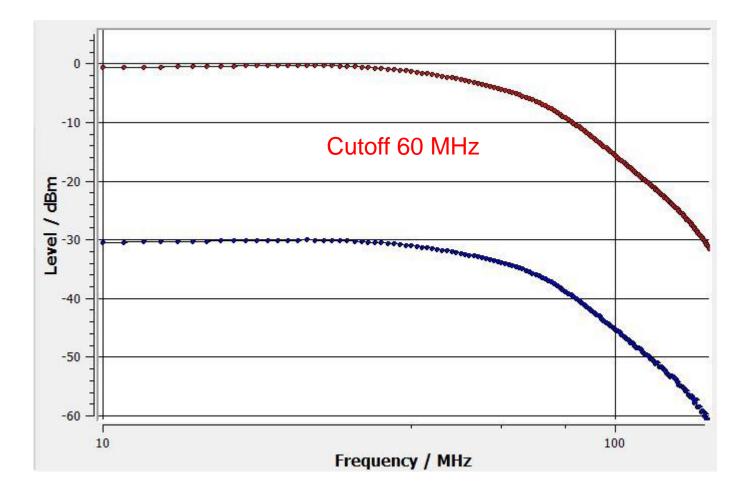

- 10 Low pass Filter (Bandwidth < 60 MHz)

- 3x2 channels to read the PMT anode signal and splitted in high (30 dB) and low (0 dB) gain + 4 single channels with possible different gain (1 Small PMT, 3 ASCII)

- Analog signal dynamic range: from 100 mV to -1900 mV (5% of dynamic reserved for the undershoot)

- 1 ms recovering time

# Specific requirements

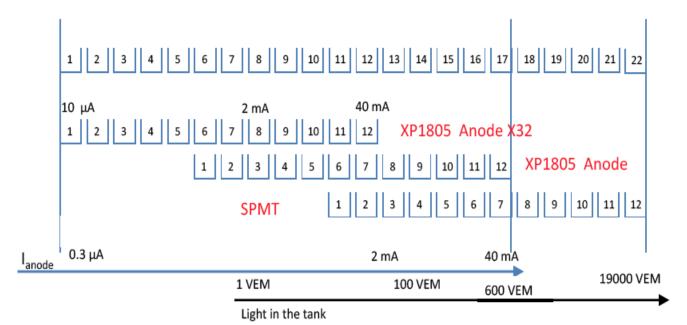

In the following scheme, the dynamic range of the new electronic is shown:

The dynamic range scheme will allow moving the trigger threshold two bits higher and increasing the current dynamic range by a factor of 32.

The gain of the PMTs will be kept the same as before, 3 10<sup>5</sup>. The muon peak will be in channel 200. An additional small PMT (SPMT) will be used to extend the dynamic range.

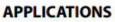

# The selected commercial ADC

12-Bit, 125/105 MSPS, 1.8 V Dual Analog-to-Digital Converter

AD9628

#### FEATURES

1.8 V analog supply operation

**1.8 V CMOS or LVDS outputs**

SNR = 71.2 dBFS @ 70 MHz

SFDR = 93 dBc @ 70 MHz

Low power: 74 mW/channel ADC core @ 125 MSPS

Differential analog input with 650 MHz bandwidth

IF sampling frequencies to 200 MHz

On-chip voltage reference and sample-and-hold circuit

2 V p-p differential analog input

$DNL = \pm 0.25 LSB$

Serial port control options

Offset binary, Gray code, or twos complement data format

Optional clock duty cycle stabilizer

Integer 1-to-8 input clock divider

Data output multiplex option

Built-in selectable digital test pattern generation

**Energy-saving power-down modes**

Data clock out with programmable clock and data alignment

Communications

5

## **Design concept and solution selected**

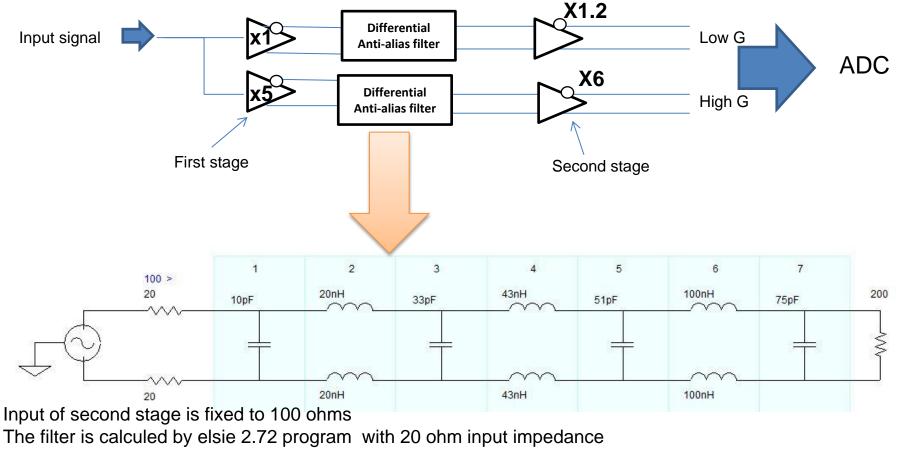

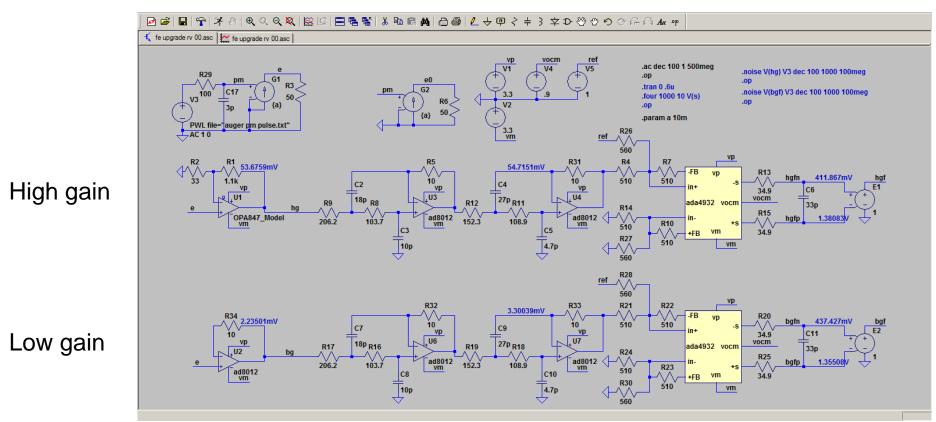

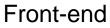

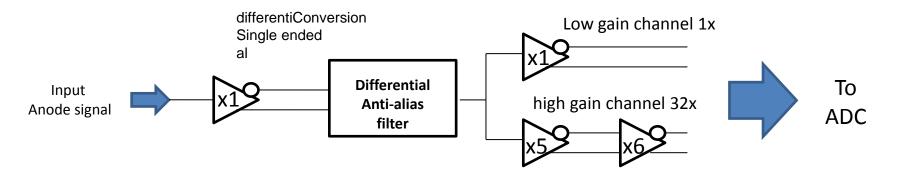

To obtain the requested performances various possibilities have been investigated. The idea is to split the PMTs anode signal in two channels: a 0 dB and a 30 dB channels. Filters for each channel will be implemented instead of a single filter for each anode to avoid to amplify the noise produced by the filters. The final adopted solution is the following:

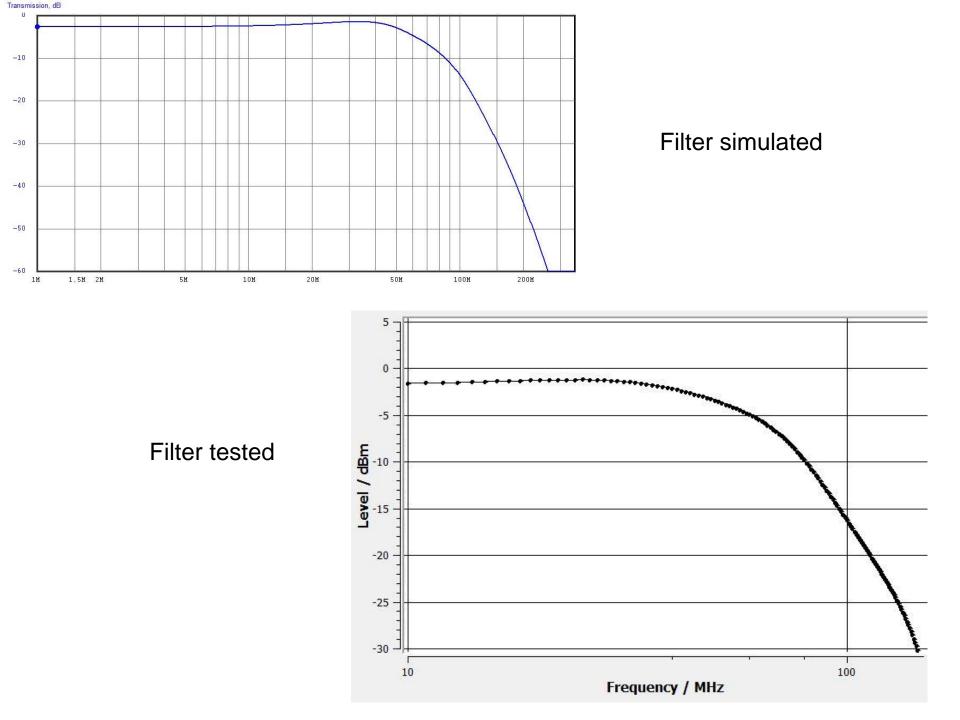

The maximum filter attenuation (in low frequency) is -2dB

## **Design concept and solution selected**

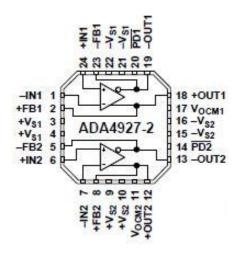

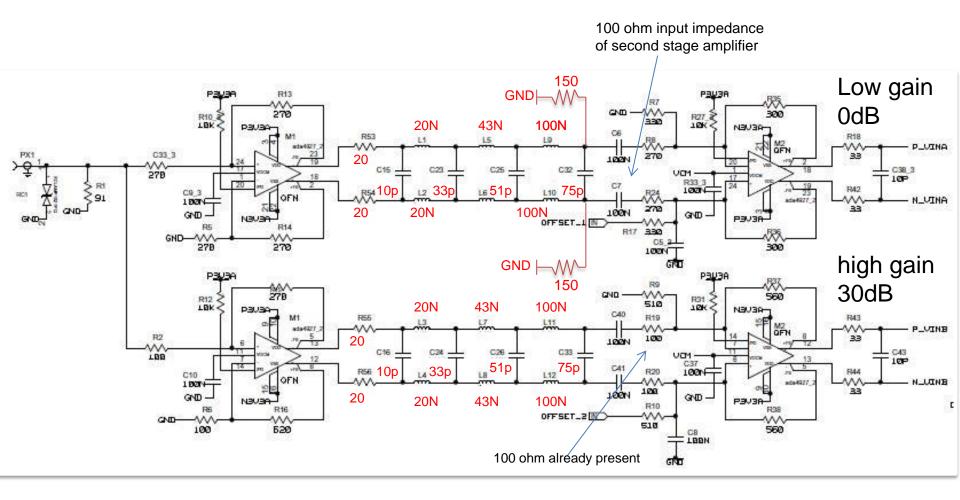

- Type 1 Input: The signal from the anode of the PMTs are splitted and amplified, by 0dB the low-gain channel and by 5dB the high-gain channel and made differential. This has been done using dual channel ADA4927 Operational Amplifier (OA). Then a 5 pole passive Low-band pass filter is implemented using inductances and capacitors. Finally the last amplification stage is implemented using the same ADA4927 OA obtaining a 0 dB and a 6 dB gain on low-gain and high-gain channel respectively. At that stage are also implemented the V<sub>CM</sub>, the common mode voltage reference, and the offset generator to make the ADC working in the correct dynamic range (form 100 mV to -1900mV)

- Type 2 Input: The same solutions are adopted with the last 4 channels but with the possibility to split a single input on two channels or using two separated channels with the amplification tunable by the choice of the feedback resistors in both solutions. One of this will be used for the "Small PMT" and the other 3 for ASCII.

ADA4927-2 is the final Analog Device microchip chosen. four stages, two microchips

Features Extremely low harmonic distorsion Very Low noise 1.4nV /√Hz Bandwith -3dB 2.3GHz Differential line drivers

# Type 1 input detail

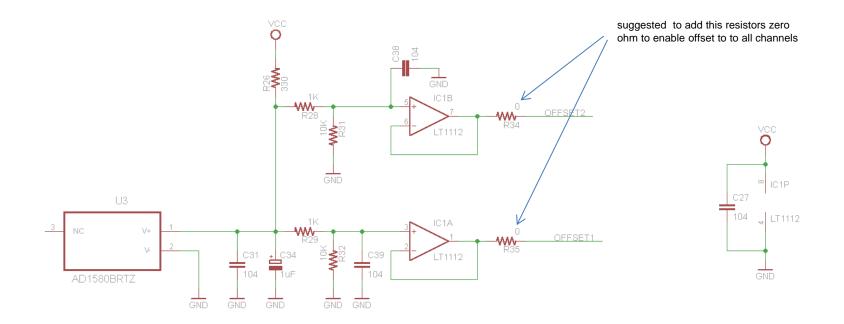

The offset can be supplied by a single generator and distributed on a common line to each ADC channel input. Due to the importance of the stability of those values, the possibility of activating dedicated offset generators for each channel has been implemented by mean of Zero resistors.

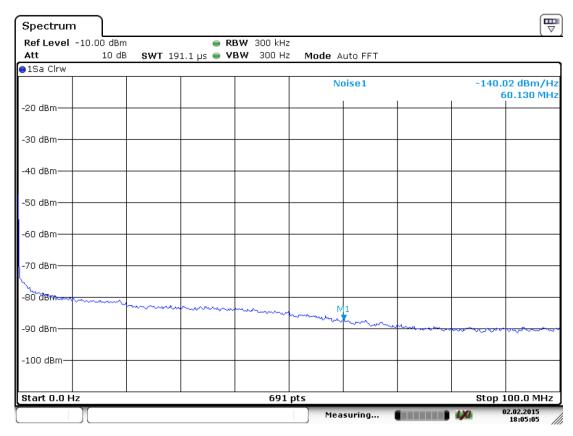

Output of twin channels (high gain and low gain) on sweep of frequency(input signal -30dBm)

## Noise and Power measurements

## Alternative upgrade scheme Hervé Lebbolo

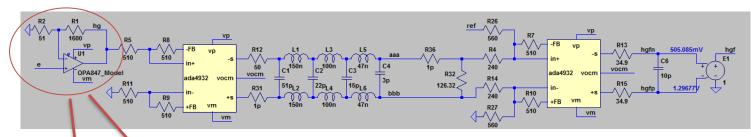

Each channel is made of one positive gain amplifier followed by a 4th order active filter and a unity gain differential ADC buffer ADA4932. High gain is made with single low noise aop opa847 Low gain and active filter with aop AD8012

## Alternative scheme status Hervé Lebbolo

First tests performed without differential ADC buffer :

High gain noise : less than  $360\mu$ V rms Low gain noise : less than  $180\mu$ V rms Power consumption : ~170mW

2.00 1000/ 300.08 100.08/ Tria'd 7400 La commande a atteint ses limites High gain waveform Measurement Menu Source Select: Measure Clear Thresholds Ampl Amp Meas

Next step : test of a complete dual channel with ADC and differential buffer.

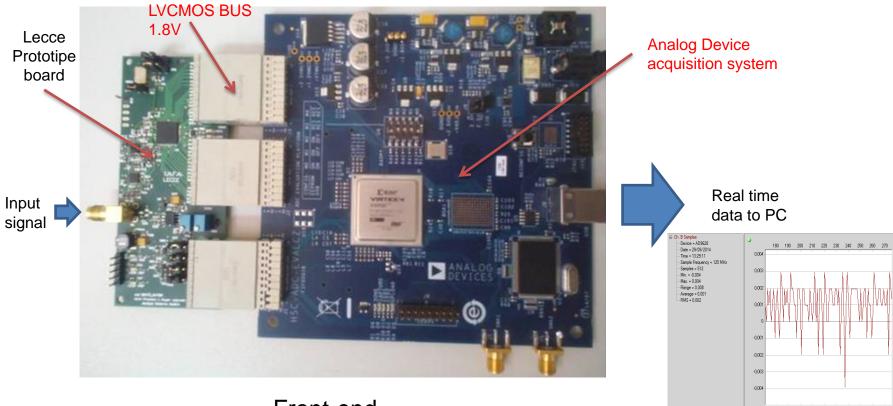

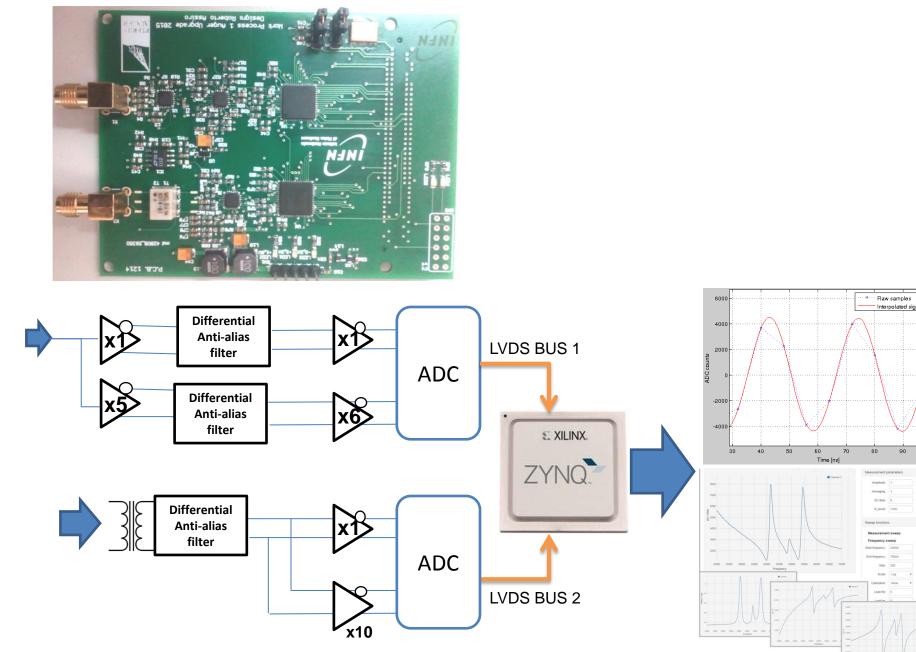

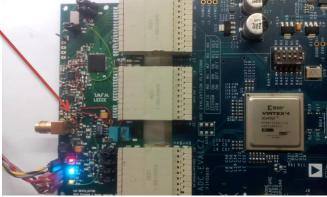

### Working Progress 1 - Lecce Prototype 1

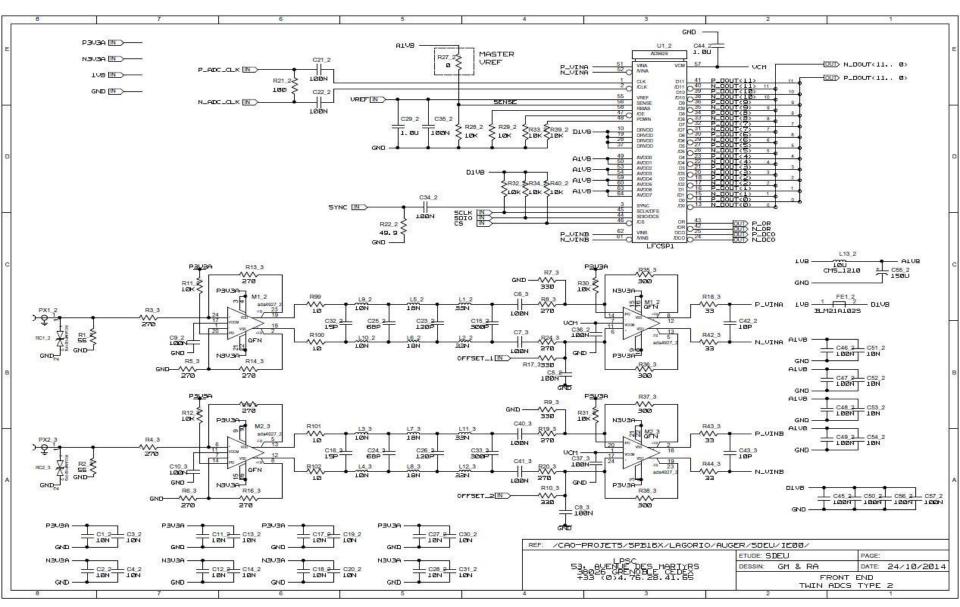

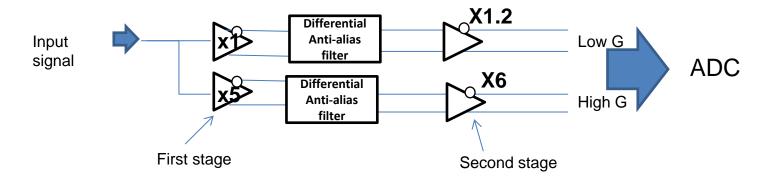

### Working Progress 1 - Lecce Prototype 2 Twin couple of ADC channels in two differents front-end solutions

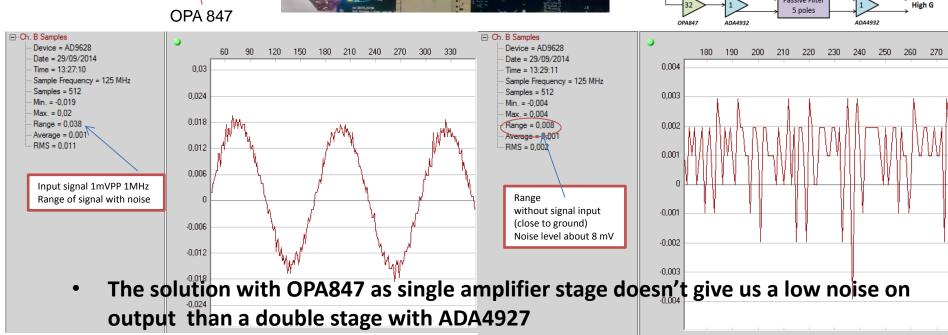

### Working Progress 1 - Lecce Prototype 2

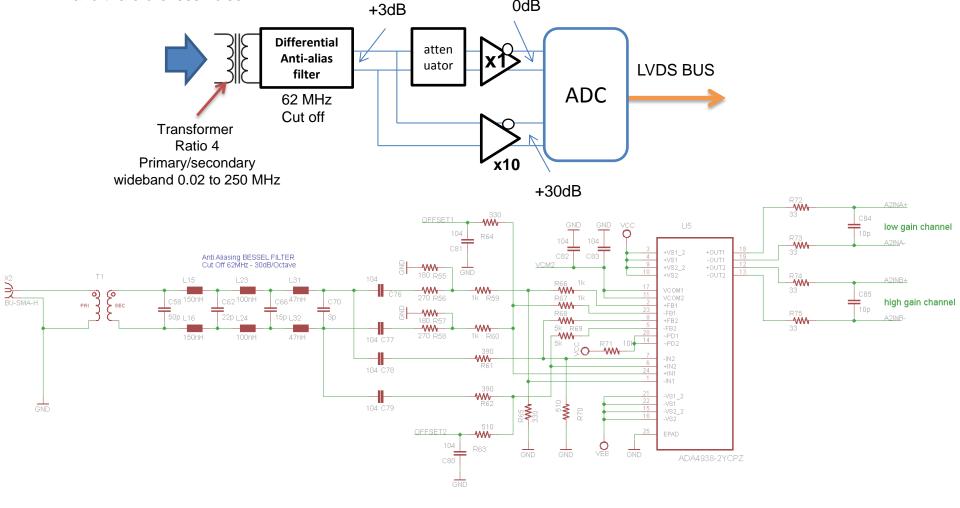

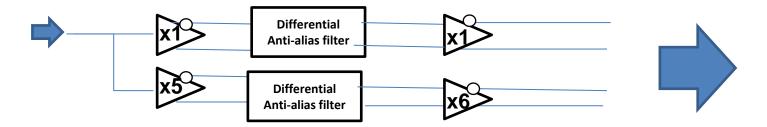

### Front-end alternative solution

Features:

- -Less power consumption. One stage for each channel

- One anti alias filter for both channels

- Less gain for each amplifier and therefore less noise

- Wideband 0.02 to 62 MHz (transformer low cut off)

In this solution we utilize the transformation ratio of the isolation transformer to get less gain of the amplifier stages and therefore less noise

• Backup Slides

#### Measures of high gain channel simulated from Hervè Lebbolo

Modifications of front-end prototype board

The proposed solution with one stage amplifier OPA847 with 32db of gain in my measurement does not change the output noise from our first Solution. Less than factor 2

It was tested with ADA4927 instead of ADA4932. May be it could be better to convert in differential (our solution) for a low noise interference before the amplification.

Passive Filter

Low G

ADA4932

First differential design proposition

IN

ADA4932

Passive Filte

5 poles

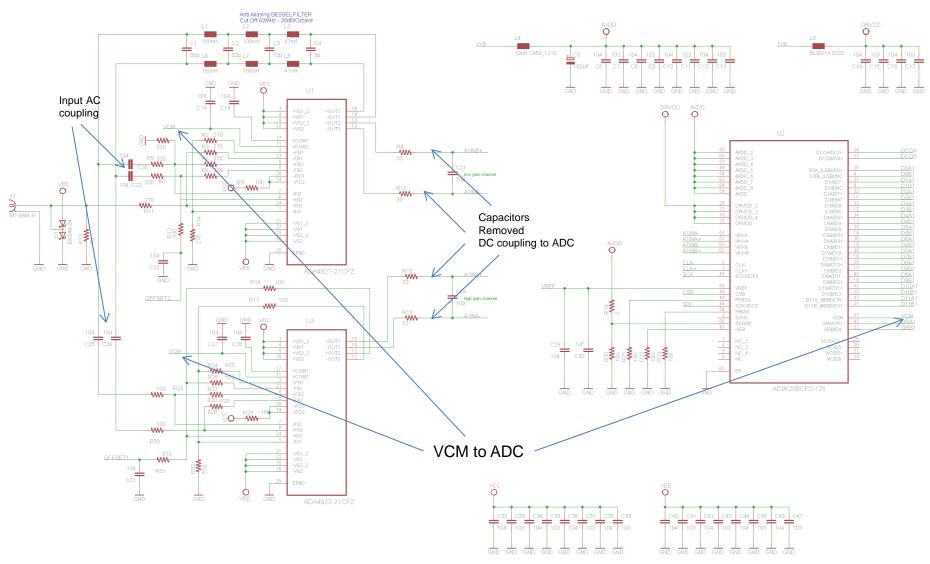

### Modifications for the offset generation

FRONT-END TYPE 1

This is the old type 1 input, dedicated to the standard photonis PMT. This configuration is affected by a noise level of about 10 mV. In order to reduce the noise an alternative configuration has been presented, involving two separated filters. The space dedicated to each channel is enough, so we suggest to implement the following:

This configuration has been tested and the measured noise level was about a factor 2 lower

FRONT-END TYPE 1 ROAWING MEDIA, PC'ER Curoff Calve - Jose Come 0000 000 cod 125\$ l ca 14. ta. 2007 A120 104 101 104 101 2210 C214 10217 10218 10,01 CME, 1211 100-7030 25 -202 6 60 50 141 品 60 60 雨雨雨雨 60.69 104 104 = 09/60 ADU O 440,3 440 440,3 440 +0671 -0671 +0671 -0677 123 (CON) 10000 1781 1781 Alter. #00.3 #00.5 #00.5 #00.5 #00.5 #00.5 #00.5 DODBOH 22 L COX. 400 400 作用から = Dis\_Likebe-tite\_protect Does\_ Does\_DOES\_ Does\_ Does\_Does\_ Does\_ Does\_Does\_DOes\_DOES DOES DOES DOES DOES DOE 104 (20) 10(810) for gar shared SO NOT THE A166. 2 14482.1 (4482.1 (4482.1 (4482.1 wa. 生まる į. 57 1944 1944 1946 1948 A12544 A00 Double filter 1 - 100 -GAL DAL 2 ine. 60 **Ö**he 68 窈 NDA4037 2YCPZ 命 WEX. AND ALIANY BERRIEL PUTER CALON REMY RESIDENCE 618 CHINET. 10 턚 100 CON CON UNI CRADE-DISCH Single handed 10000-1005 1005 1005 а, high gais channel -1000 1.0 510 **課の課の課**の splitting 10 .81344 맥 125 92 13 194 -0471 -0475 -0672 -0673 사람() 4년 4월 4월 AD963HBOPE-125 应 \$ 命命命命 æ R205 459 R254 459 R254 icon icon icon icon icon icon 100 #356 「相比の何 600 H.223-Ko W of 9 -10 kait 100 8 1999 GERRETI . WW 10 817 C/R 817 ସେ ସେ ସେ ସେ ସେ ସେ ସେ යන් යන යන යන යන් යන් යන් යන 18 101 2 575 杰 南 AC44077-2VCP2 (ho 病病病 යා යො ゐ

## Conclusions

Voltage reference is very important for the precision of analog conversion

Internal ADC generator for the common reference is a solution with very low thermal drift and the error for the load current (five ADC) is about 0.5 % (5mV on 1V)

The solution with external generator must have better features than internal generator and the circuit should be appropriate and stable. The proposed external circuit solution requires an appropriate thermal exscursion test. However, a solution with external generator could be provided and not mounted on the board.

The 2 filter configuration has a factor 2 less noise, so it is recommended. Other options discussed in Grenoble have been tested, but the result are not satisfatory

We started working on the spi driver to be implemented in the zynq. We bought Zedboard with the zynq7000 evaluation board.