AGATA AMB Phone conference 25<sup>th</sup> March 2022

## Apologize:

## ASC Report / ASC Matters

## MoU

The phase 2 MoU is in operation. The final signatures from Germany are in progress. GSI has signed and it is with BMBF for signature. Germany has signed a version with a change in the main text relating to cost overruns and the tables defining the resources required have separated the GSI and BMBF contribution.

ANNEX E, which specifies the common account procedure for operation costs, has been signed by France (CEA, IN2P3), Hungary (Atomki), INFN, Spain (CSIC, Salamanca, Valencia) and UK.

The bank details in this have recently changed from CNRS to GANIL. This change requires an amendment to the MoU since it affects one of the clauses in the MoU as well as the bank details. IN2P3 have sent an amendment, which they have signed. Bulgaria (INRE-BAS), Hungary (Atomki), Italy (INFN), France (IN2P3), Poland, Spain (CSIC, Salamanca and Valencia) and the UK have signed this amendment. All other Parties have been sent the amendment.

## ARRB

The new AGATA Resource Review Board (ARRB) has been set-up. A start up meeting (remote) took place on 2<sup>nd</sup> March 2022.

In attendance Present: Maria Yavahchova (INRNE, Bulgaria), Ari Jokinen (Jyvaskyla, Finland), Marcella Grasso (CNRS, IN2P3, France), Franck Sabatié (CEA, IRFU, France), Zsolt Dombrádi (Atomki, Hungary), Rosario Nania (INFN, Italy), Adam Maj (COPIN, IFJ PAN Krakow), Pilar Hernandez (Spain), Bo Cederwall (KTH, Sweden), Karen Clifford (STFC, UK)

AGATA Representation: Angela Bracco (ASC Chairperson from 4/22), Emmanuel Clement (Project Manager), Andres Gadea (previous Project Manager), Benedicte Million (Resource Manager), John Simpson (ASC Chairperson).

Paperwork provided to the board included the names of board members, terms of reference as defined in the MoU, the MoU with signatures, the international review and the presentations for this meeting.

J. Simpson gave a presentation on the status of the project, the MoU and introduced the role of the ARRB.

E. Clement presented the resource status and project plan.

The board agreed to meet bi-annually with meetings arranged following the ASC. It was agreed to hold the next meeting in late October early November. However, if the collaboration has information and key updates a meeting can be arrange in May this year.

It was agreed that the Chairperson should rotate every 2 years. Rosario Nania agreed to be the Chairperson for the first two years and he has been invited to attend the ASC.

## **ASC Meetings**

The next ASC is 31<sup>st</sup> March (Zoom) then12/13<sup>th</sup> October 2022 in Milano.

## ACC Report / ACC Matters

J. Freeman is the new representative of the University of Manchester. Reminder, ACC meeting on the 10<sup>th</sup> of June after the AGATA Week. 10Y anniversary session on the agenda of the ASC meeting.

## LNL Status (J.J. Valiente-Dobon)

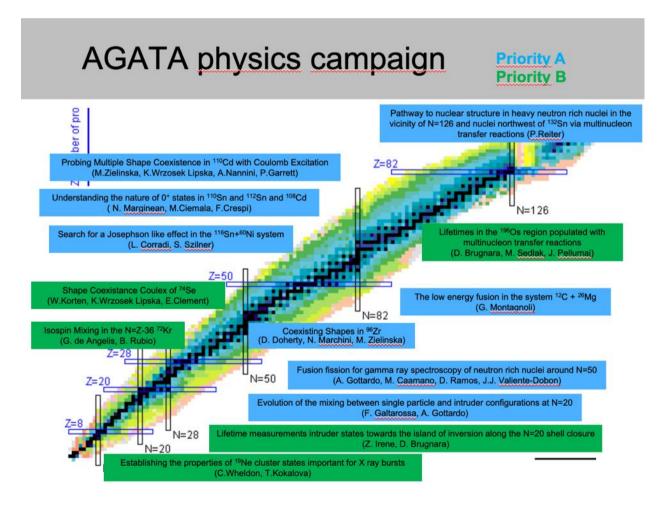

In the following one can see the experiments approved in the PAC February 21-22-23, 2022.

The First commissioning (PRISMA) will be around the 26th of April. The second commissioning (SPIDER) 20th of May. Third commissioning (inversed plunger) 21st of June. Final schedule will be public in a very few days. First experiment will be as early as end of May.

- Unfortunately, we have an issue in ATC15 has a cold point, see picture:

- Currently we have 7 ATC in the structure. A picture containing indoor, different, several, variety Description automatically generated

- One detector is biased. tests will start today and next week. Once the LN2 control system is fully upgraded we will biased all.

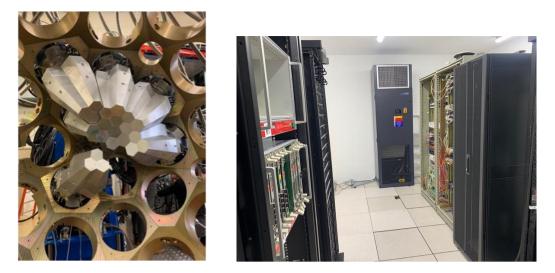

- Sala Vax is ready. We are installing the GGP machines, disk servers, services and the GTS tree. The ancillary machines will be installed next week. On Monday colleagues from Orsay are coming.

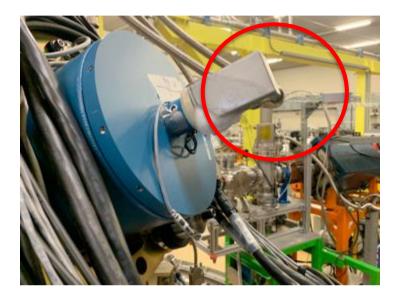

- Issue with the bayonets. We are trying to solve the problem with a small change. Picture shows a prototype.

A close-up of a machine Description automatically generated with medium confidence

LN2 price might increase even by a factor of 4. We are under discussion with the Linde company that is the provider.

We had a meeting today 25/3/2022 regarding the ongoing upgrades of the LN2 system. They will be visiting us from the 11th to 15th of April.

Nabil Karkour will let me know the dates of his visit before the commissioning.

AGATA week 6th of June: https://agenda.infn.it/event/30320/

We have created the indico web page. Should we do some official announcement? NIM for the LNL installation ongoing.

## GSI Status (K. Wimmer)

Starting to investigate the mechanical installation in collaboration with Daresbury.

## **REPORTS FROM THE WORKING GROUPS**

## **Detector Module (H. Hess)**

## **Status of the detectors:**

56 detectors available within the AGATA comunity

## **MIRION:**

15 detectors delivered to Mirion end of July for annealing due to neutron damage

On 4 detectors some problems were found

- A003 with 940 pA @ 5kV -> leakage current, under repair

- B008 -> leakage current on F2 inside a spectroscopy test cryostat

- After annealing this detector was fully functional, no leakage current was observed, delivered to Cologne in Dec. 21

- B016 with 300 pA @ 5kV -> leakage current

- Repaired and delivered to Cologne, FAT 16 Dec. 21

- C005: one sector is missing at warm temperature but there, once cold.

- Such failure is new

- No leakage current

- Under repair

Order for the repair of A003, B008, B016 and C005 placed by KTH (for B008 just the annealing is invoiced)

Remaining 11 detectors annealed successful, efficiency between 71% -79%, resolution within specs.

B012 and C015 were delivered in Dec. 21 for repaire due to leakage current

- B012: leakage current at the factory was positive

- $\circ$  Due to the experience with B008 the detector was annealed at 100 °C

- After annealing measured in test cryostat, no leakage current observed

- Two to three thermal cycles will be performed as a stress test to investigate the behaviour of the capsule

- C015: Leakage current check at the factory -> capsule shows no leakage current at Mirion

- $\circ$   $\,$  Due to the experience with B008 the detector was annealed at 100  $^\circ C$

- Test in a test cryostat, everything is ok

- Two to three thermal cycles will be performed as a stress test to investigate the behaviour of the capsule

It seems that sometime when the capsule exhibits leakage current it does not necessarily require to reprocess the HPGe but a reprocess of the capsule environment,

through an annealing like procedure, might be enough to recover the performances. This is hypothetic at the moment, is under investigation and has to be confirmed in the future.

In the moment 4 detectors are a Mirion B012 and C015 for further diagnostics and A003 together with C005 for repair.

Furthermore, Mirion delivered 3 repaired detecors C001 (FAT Dec. 21), the DEGAS detector B501 (FAT Dec. 21) and S003 (FAT Dec. 21) and 3 new detectors B019 (FAT Sep. 21), A018 (FAT Oct 21) and C019 (FAT Oct. 21). Owner of the three new detectors A018, B019 and C019 is the University of West Scotland (UWS)

## Saclay:

In the moment 4 detectors are at Saclay to confirm the diagnosed problems while mounted in different ATCs

- A007, A012, C003 leakage current

- C014 high voltage problems

## Liverpool:

2 detectors for scanning

- A009 scanned before annealing and now after annealing, scanning ongoing

- C017 scanning ongoing

#### Salamanca:

1 detector for scanning

• A005 comparison of the performance of the different scanning tables

#### **Cologne:**

7 detectors

- B002, B005, B008 & B016

- A018, B019, C019 will be mounted by CTT in a new ATC

## **IPHC Strasbourg:**

2 detectors

- B005, C001 assembly of the motherboards for cold preamplifier

- Meanwhile in Legnaro, will be mounted in ATC12

## Status of the AGATA Triple Cryostats at INFN, Legnaro :

## **Fully operational:**

7 ATCs fully operational (resolution at 1.3 MeV)

- ATC03 Core: A002 = 2,31 keV; B007 = 2,23 keV; C007 = 2,55 keV

- ATC07 Core: A015 = 2,52 keV; B014 = 2,30 keV; C008 = 2.53 keV

- ATC10 Core: A011 = 2,22 keV; B007 = 2,36 keV; C012 = 2,34 keV

- ATC14 Core: A014 = 2,26 keV; B010 = 2,45 keV; C016 = 2,27 keV

- ATC15 Core: A013 = 2,31 keV; B015 = 2,28 keV; C011 = 2,14 keV

- ATC17 Core: A016 = 2,18 keV; B017 = 2,18 keV; C013 = 2.27 keV

- ATC18 Core: A017 = 2,28 keV; B018 = 2.48 keV; C018 = 2,24 keV

## ATCs with problems:

- ATC01 several detectors were replaced due to leakage current and high voltage

- Detectors mounted: A010, B011 and C009

- Segments C1, C4 and C4 on detector C missing

- ATC08 was in Cologne fully operational over 9 month

- Detectors mounted: A006, B013 and C008

- Oscillating

- Detector B is tripping while increasing HV and at nominal Voltage

- Will be reworked in Cologne

- ATC09

- Detectors mounted: A001, B001 and C004

- Core on capsule C wrong gain

- $\circ \quad \text{Reason is probable the Core FET}$

- ATC11

- Detectors mounted: A004, B004 and C010

- Oscillating

- If core warm preamplifier is removed or disconnected oscillations removed

- ATC06

- Detectors mounted: A008, B009 and C002

- Oscillating

- $\circ \quad \text{On detector C core signal missing}$

## CTT:

The assembly of ATC19 is postponed due to COVID-19 infe

#### Infrastructure (B. Million)

Last meeting: March, 7<sup>th</sup>, 10<sup>th</sup>, 25<sup>th</sup> Next meeting: April, 1st In LNL: April, 11<sup>th</sup>-15<sup>th</sup>

## New developments status (Saclay): New LVPS:

New LVPS group for 8 ATCS New LVPS installed on Profibus. Profibus.

3 Old LVPS for 3 ATCs Old LVPS still to be installed on

Under test with new AUTOFILL: New LVPS working fine, old LVPS to be checked as an upgrade was added to the PLC.

#### New Autofill:

- Autofill Control (PLC)

- Electrotechnics

After February visit: long time stability test on-going. PLC and alarm issues (cryogenic process and dialer communication) fixed this week remotely: new version of the PLC

yesterday afternoon. Tests of the new PLC program version ongoing in LNL. GUI problems to be fixed during next visit.

Next visits to LNL: 4 people from Saclay in April,  $11^{th}$  - $15^{th}$  for finalizing critical aspect of the functioning and of the GUI.

September if needed: to insert last connectors with corresponding final test Need for new Bayonets: see Javier LNL report

**Purchase:**

New bayonets: being discussed

New LVPS: in 2022 40 capsules (13 ATC) at max?

Project definition planned substitution of all LVPS for up to 75 capsules (25 ATC) within 2024. This means we will need to have 3 new ( $36k \in /cad + 20\%$  discount for volume production) + 1 additional ( $18k \in$ , Staying in Saclay/AXIS) LVPS groups at that time. When do we, as AGATA, prefer to buy them?

- Mechanics:

Last meeting: March 17<sup>th</sup>

Test with dummy detector adjustment of alignment rings with new masks to prevent scratches and laser tracker and **extra threaded adjusters.**

Very busy environment. detector survey tooling

First 3 detectors mounted 400µm between 2 detectors

Many upgrades for a smoother procedure. In particular the combination of extra threaded adjusters on the rings and the detector survey tooling provided us with the tracking and control needed to achieve the close to uniform clearance between detectors.

Still some improvement foreseen to achieve fully uniform clearance between detectors.

Rotation Test: clearance of 0.35mm between 2 ATC becomes 0.5mm after rotation by  $70^{\circ}$ .

Very good collaboration between local, STFC and GANIL mechanics teams. STFC team requested a feedback for the Lab, that I was very happy to send in the name of the AMB.

To be done: Check alignment of surfaces against CAD Update the mounting document

#### - DataBase activity:

Last meeting: March, 17th

list of unused material inserted in DB:

2 groups of VCC + PBC crates lent to EXOGAM

1 group of VCC + PBC crates is being lent to DEGAS

$\rightarrow$  material has been sent to GSI on 18/3.

OS preparing possible insertion of warranty information on capsules INFO requested to HH

Visit to LNL: March, 29<sup>th</sup>-31<sup>st</sup> to adjust and complete DB as much as possible

Do we want to have the DB available on the public AGATA website ?

https://www.agata.org/metabase

## Front End Electronics (A. Gadea)

#### Trigger and clock distributions.

The new GTS trigger processor from GANIL has been delivered to AGATA at LNL with documentation.

All are open sources.

GTS Leaf firmware : <u>https://gitlab.in2p3.fr/Ganil-acq/Embedded/Modules/gts\_mezzanine</u> GTS TP firmware : <u>https://gitlab.in2p3.fr/Ganil-acq/Embedded/Modules/GTS\_TP</u>

#### **DIGIOPT12 Digitizers (A.Pullia)**

Completed the production of 16 core boards from UK order. Issues during the factory test due to short-cuts at the level of the connector. One repair yield 100%. Boards delivered to IFIC/ETSE Valencia for CAT. 11 already tested and the CAT will be completed except the burning test that will be done later. Preparation of the new INFN order for DIGIOPT12 boards ongoing. As soon as the order is place the company will start the procurement of 1000 ADC chips. Procurement of the FADC still without new from the provider or produced and still with the 52 weeks lead-time. In February, the order from INFN-Milano was on-going the administrative procedure, expected ready late February or March.

During 2022, it will be done the re-design of the DIGIOPT12 boar to use an available FADC, in case the original FADC can't be procured. Using CAD project converted from Zuken to Eagle software. New digitiser control scripts will be need at some time in the future after the hardware changes. The conversion from Zuken to Eagle was completed in 2019 this opened the possibility to modify the routing for the phase 2 DIGIOPT12 production and now will allow to change the design of the DIGIOPT12 with a different FADC

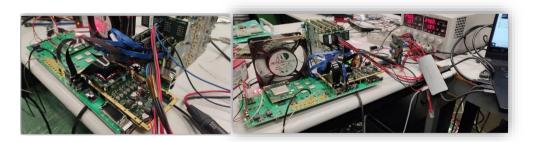

#### PACE pre-processing board (J.Collado)

The new prototype seems fully functional, no problem found so far and Slow control completed, probably required HDMI correction for the clock transmission. Many discussions on the SFP connector cage and spacers for the present layout of STARE prevents preventing a good connection in the FMC connector. Further discussions took place on the 8<sup>th</sup> of March and agreement was found on the mechanical inaccuracies. Now discussion more oriented to the signal or clock transmission. Javier Collado will visit Orsay, starting on April 4<sup>th</sup> to check the signal transmission issues. Note that the error is now of the order of 10<sup>-8</sup>, but still is desirable to have a further reduction.

Trenz has announced large delays in the production of the TE0808 needed for the PACE preprocessing board, the TE0808, nevertheless, 37 have been already delivered. The undelivered TE0841 for STARE will also suffer from delay, but we have already more than 45 boards delivered (11 KTH + 20 UK + 14 IPHC) One component missing, only available from brokers, to be discussed in the RM contribution.

Power and Temperatures checked and within expected values. Ready to test mechanics and cooling, possibly next week.

COA Adapter Status: Validation Completed. Data reception checked for Core and segment DIGIOPT12 ADC channels. Mechanical issue corrected. Ready for production: Production run 150 Segment + 50 Core

#### STARE (N.Karkour)

Xilinx licence is now installed and tested in the laboratory. It is proven to work for over 10 hours unlike the evaluation code used earlier which stops working after a period of time.. STARE is under production, some component deliveries summer 2023.

Funds available for production (O.C. + Investment) €40k Orsay €30k Sweden, IPHC, York. The quotations will be sent soon by the manufacturing company

Test bench ongoing: Interface board under production. 20 Trenz SOMs delivered via GSI after procurement by University of York. Software updates under way including modifying the buffer size and also testing whether one server can receive data from 2 STAREs checking dead time/loss/error rate

#### Mechanics and PSU (V.Gonzalez)

Personnel available on contract for the AGATA production for 50 units. New 3D printed model is complete for front panel with connector holes updated and LED light guides checked PSU unit- DIGIOP12 don't get 3.3V, instead get 3.0V. Sense lines are missing but could be retrofitted. Final power supply design is waiting for end to end test results. All components have been procured for 50 units.

#### Test bench (J.Collado)

Presently, a complete prototype electronic chain is set in LNL. The Phase2 firmware for processing (CAP) is not available (see next section) and a bootstrapped version is used to perform an end-to-end data transfer from digitizer to workstation via PACE and STARE.

After a long stay at LNL, Javier Collado is visiting GANIL to gain experience on GTS, SMART and the MWD implementation for EXOGAM2 on week 12 and 13. The plan for the time in GANIL is to start producing GTS firmware to test the implementation of the GTS Hardware in PACE. At GANIL first discussion with Gilles Wittwer about SMART

status and whether SMART integration can be anticipated alongside GTS will be organized.

GANIL team are ready to help JC with the GTS integration and getting the MWD and trigger module from GANIL numexo2 board.

J.Collado showed a possible plan for his work based on available time (not work needed, that will be evaluated only after his visit to GANIL):

1) Multi Buffer Lane: 1 to 2 months

2) Trigger CFD and Energy (MWD): 1 to 2 months

3) GTS And readout control: 2 to 4 months

4)Development of Test System: 2 months

$\rightarrow$ Expected delivery at the earliest: Christmas 2022.

J.Collado is starting to measure SNR in the full system- initial results look the same as v1. Expected to perform the test in the coming 2 weeks.

For end to end tests, the detector can be ready but pulser data not yet taken.

IJClab has code ready to transfer 8k memory buffer in place of local software pulser to generate data to go to Aurora Link.

J.Collado found some transmission issues when sending the buffer to the Aurora link, the problem was solved mid March. Except for a periodical de-alignment of transceiver between DIGIOPT12 and PACE, all the chain is ready to take data. Issues have been found when trying to write data into the server disk. All the performance test firmware was ready by week 11 although the data losses noted above are yet to be debugged

The data will be compared with the Phase 0 electronics.

Energy resolution will be determined from long traces, to be acquired for both core and segment channels. Short traces of events will be available for PSA performance evaluation.

Plan:

Week 12 and 13: Presently the test has been interrupted to be able to test the GTS hardware, adquiring know-how in a visit to GANIL

Week 14: will be devoted to the error rate reduction in the transmission PACE - STARE Week 15-16: the aim is to test with external data from digitiser with pulser and detector. The key part of the test is end to end ENOB with copper link from digitiser to server.

Summarizing the aims of the test:

1) No data loss

2) Complete detector, all segments, 1us each one in server

3) Long traces (even if segment by segment) for MWD setup and Energy determination Buffering currently uses 8K for AGATA compatibility (software limit only- can be increased to 200k). Software data validation to qualify the data expects 8k buffers (while maintaining 10Gbps rate).

Test bench status is the following (18<sup>th</sup> March 2022)

## Hardware

#### PACE-CAP power and Boot FPGA: Working

• minor problems in the PACE-PSU communication that have already been solved and set for the production version of PSU  $\checkmark$

#### **PACE-CAP Slow control: Working**

- External from FPGA processor/UART until IP bus is properly implemented

- Issues found on HDMI, already corrected  $\checkmark$

#### PACE-CAP-STARE: Working. issues on the transmission (BER <10^-8)

• Unknown origin - Suspects are coupling capacitance and connector spacing

#### PACE-CAP-Digi-Opt: Working. issues on the transmission (BER <10^-6)

• Clock related problem (working on now)

#### PACE-CAP-GTS: To be tested

- Clock system delay

- GTS transceiver

#### PACE-CAP-Ethernet 1G: Basic test done (PHY response)

- PHY response √

- Need test with real communication to mezzanine processor

#### PACE-CAP-SD: SD card reading

• Start linux on SD

#### **Firmware/Functional Test**

Sending basic test data from PACE to STARE link√ Writing simulated input data from PACE to STARE link √ Writing digitizer data on buffer to STARE link√ Extracting baseline data noise from digitizer (Working Now) Writing data buffer on STARE from digitizer with external pulser (Working Now with BER rates noted above) Writing real data from detector to STARE link

# Current Firmware PACE-CAP

- Data receiver

- Transceiver

- Deagregator reproduces jesd204 data recovered from TLK agreggators

- Reorderer reordering layer to proper channel number

- JESD204 AGATA custom Custom made (lower resources and link stabilities)

- o JESD204 Xilinx Xilinx original IP (excessive complexity for AGATA channels)

- o JESD204 data simulator (Simulates JESD204 modules data Buffer/Step/101)

- Elastic Buffer (working, but further work has to be done to auto calibrate signals)

- Stream output formatter

- Data measurer data qualifier for received ADC stream data

- Trigger detector simple CFD

- MultiBufferLanes Buffers up to 16k samples of data for all lines, communicates with AGATA-STARE link in AuroraQuad, possibilities: Selected 4ch long trace (triggered and untriggered)/ All channels 200s (triggered and untriggered)

- AuroraQuad

- Quad link Aurora transceiver

- Data generator for STARE with counter

- AGATA-STARE link for MultiBufferLanes transmission

- Simple timestamp generator

- GTS transceiver simple test

- Sync Pattern control (to be adjusted with Elastic Buffer for autocalibration)

• System monitoring (Low level monitoring ILA/VIO Xilinx, to be removed in the definitive version for the real monitoring system)

#### **BOOT-FPGA**

- Auto start PACE-CAP

- UART communication (Bus to I2C)

- Slave I2C for SC-FPGA

#### SC-FPGA

- Automated startup needs help from UART/Processor from the momento

- Register Map

- I2C/SPI/uWire/MDIO/IO communication and register Map

#### **Firmware Status and Discussion**

As previously reported, there is a severe issue with the firmware development at IPHC. No IPHC firmware has been made available to the collaboration. The funding for a part time AGATA firmware engineer at IPHC was not funded by IN2P3.

In autumn 2021, IN2P3 has appointed Ph. Vallerand (IJClab) as CNRS AGATA Technical coordinator, supervising the task devoted to IN2P3. He received from IN2P3 a formal letter of mission and can act formally toward the technical teams of CNRS involved in AGATA.

IPHC was in charge of providing the firmware (CAP) of the processing board PACE. This means gathering together the SERDES part (delivered by IFIC), the MWD and trigger block (IPHC), the GTS IP (delivered by GANIL), readout-control, event building and data formatting toward STARE (delivered by IJCLab). It was planned to use the MWD code available at IPHC. The IPHC modified-GANIL-GTS and IP bus bridge code was delivered but needed to be checked to see if it can be used. This was not achieved. The remaining blocks have not been presented or distributed to the collaboration. Early 2021, IPHC announced that the firmware team is not working anymore for the AGATA collaboration due to conflicting commitments.

After several months without any possible interaction, it was committed in October between the PM, the AMB and the IPHC managers that the developments will be available to the collaboration for Mid-November 2021, as it is, with the proper documentation for evaluation. A particular focus was put on the delivery of the MWD (energy calculation) and Trigger (time calculation) blocs considered by both parties as the minimum to be delivered and to be acknowledged by the collaboration. Assessment criteria were generated by I. Lazarus in November 2021 to be applied to check for portability. In addition, the functionality will be checked for compatibility with AGATA.

On the 13<sup>th</sup> of January, Ph. Vallerand went to IPHC for a face-to-face meeting. The statements from IPHC is the following. IPHC claims that the development of the deliverables is in progress but it takes time because the source codes will be delivered according to rules which will allow him to ensure the ownership of his work and also not to be criticized by the other engineers involved on the " firmware". For explanation, IPHC specifies that in November and December, he took training and was 50% involved in CMS. Concerning the codes developed, IPHC has chosen to constitute a library of cells making the code independent of the hardware and which will facilitate future modifications. Based on its experience of working with the electronic group of CERN, IPHC wishes to provide generic codes developed and documented according to these methods. It was also reported that IPHC is still working for AGATA (20%) and in

particular on the data format out of PACE but without following the standard imposed by the collaboration.

However even after the meeting, the AMB never received any report in 18 months on these activities. Not a single files of firmware needed to progress in the development was delivered and there is no way to know how compatible is this work with the progresses made by the collaboration. It was always stated in our exchange that the IPHC contribution is welcomed if it is following the collaboration standard. It was noted that IPHC needs to be involved on terms defined by AGATA and work on what AGATA needs in the current firmware scenario rather than continuing the previous scenario where he was providing most of the firmware. The first step is to see what is in the existing codes that IPHC has completed (e.g. MWD). Buffer codes need to be well defined at the interfaces, both at the port and protocol levels because there has been some discrepancy here between that AGATA standards and ideas from IPHC to implement alternatives

There was some discussion inside the AMB about how to manage the AGATA firmware development and how to avoid duplication now that IPHC is claiming a 20% involvement on AGATA firmware. In the last few months when the IPHC firmware was not made available to AGATA on the promised dates in October 2021, work has started on alternative firmware codes. After several attempt to interact until end of March between Philippe Vallerand and IPHC, the situation is the following.

- No firmware was made available by IPHC to the collaboration

- There is no participation of the IPHC firmware team to any of the collaboration meeting

- No report are received

- There is no way to know what is the status in IPHC

We consider now that the situation is a severe blocking point of the project and propose to abandon the IPHC participation to move on. The development will be refocused on the Valencia participation supported by IJCLab and GANIL.

Another proposition is to reinforce the Valencia team by supporting a short term contract from Operation Cost ( $80k\in$ ) for 18 months.

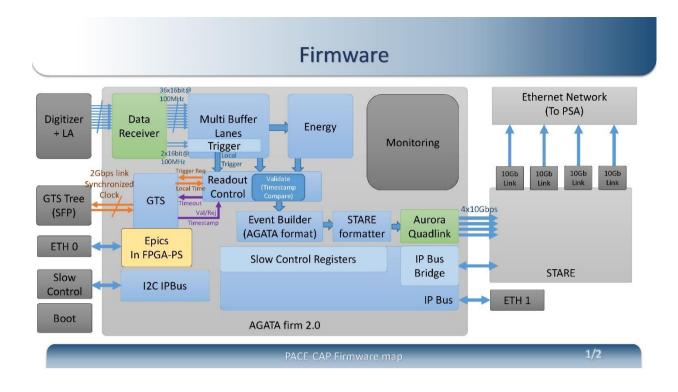

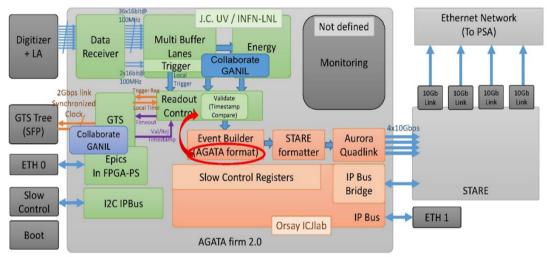

An updated diagram of the firmware is shown in the figure below.

IJCLab proposed to explore a possible collaboration to supply some of the phase 2 AGATA pre-processing firmware by writing new code and by porting/updating existing firmware. This would need approval from IJCLab director and further discussion with IJC Lab engineers about the time needed and their availability. The idea will be that IJCLab works on areas of the firmware closely related to STARE code to capitalise on investment and work already done. This covers the IP bus bridge and slow control register, the Event builder, the STARE formatter and the Aurora Quadlink.

N.Karkour presented the proposal for IJClab to work on AGATA firmware last March. Decided that IPbus can be connected to Ethernet via 10G Ethernet link using existing code, with spare SFP in STARE. Know-how, on how to implement the IPBus slaves, will be transferred to J.Collado. The IJClab proposal for the event builder and STARE Formatter with conversion to AGATA Format is to move the AGATA formatting to the Readout Control, adding 5 or 6 words in the buffer rather than an additional step that requires double memories in the FPGA. The STARE Formatter/Aurora link already exist. Needs further discussion with J.Collado because this generates more work for IFIC. IJCLab workload estimate about 2.5 months' work is needed for the remaining STARE firmware in the plan described here.

Within the partnership proposal, IFIC would supply new code and port/update existing code for Data receiver, multi-lane buffers, trigger, energy, GTS, readout control, EPICS in FPGA, and I2C-IPbus as GANIL would supply the proper GTS-IP, GTS control, MWD and Trigger IP from the numexo2 project.

The global integration will be of the IFIC responsibility with the collaborative support of IJCLab and GANIL teams.

<u>IFIC + help by GANIL</u> 1) Multibuffer + DCFD + MWD + (local Trigger + Energy management) (note that it has to be done considering the future monitoring at each step, i.e. raw traces, CFD, MWD, Local Trigger) 2) GTS + UDP/EPICS interface in the FPGA-PS linux CPU 3)AGATA formatter/event builder + Read-Out Control - Management of buffers + Validation/Rejection/Timeout 4)PACE I2C IPbus interface (only slow control PACE IPbus interface)

#### <u>IJCLab</u>

STARE formatter (creation of the STARE buffers, receiving the formatted AGATA complete events. We need as well one for the monitoring)

Aurora Quadlink for the data transfer and Monitoring (Note that only 3 SFP+ will be available and some of the work is already done for the test. It should be considered the monitoring buffers)

IPbus Bridge and register server for the control of PACE.

Also, we propose to review the leadership in the firmware task supervising the final coupling with interfaces, test and validation of the PACE-CAP-STARE system.

The following figure is a tentative distribution of the work between Uni. Valencia, GANIL and IJCLab.

Regarding the monitoring/visualization, it needs access to all code modules through welldefined ports to select the data to be multiplexed onto output data streams. The data transfer requires an agreed protocol for the 10Gb link to transfer the data to visualisation software in the server, including channel ID and timing data to allow multiple visualisation channels to be aligned. It was agreed that monitoring VHDL could be written by either J.Collado or as part of the IJC Lab contribution, both options are open at present. Nevertheless, the buffer management, Energy and time determination will have available the corresponding ports to provide the monitoring data.

#### Software (N.Dosme)

Data management on the computer side and topology manager for PACE card have been done. Expected to test the topology this week.

PACE Slow control- register list and sequences are still being prepared by J.Collado

A.Goasduff has sent description of GTS control via IPbus. New GTS format is being integrated into the slow control for new configuration files.

## Data Processing (O. Stézowski)

## **Coordination:**

Last VC meeting March 09<sup>th</sup> 2022, Meeting dedicated to Phase1 actions + phase2 actions

Next scheduled beginning of April after re-start of the DAQ box at LNL

Phase 1 :

•

- VAX room operational, Racks installed this week

- Eric and Patrick (+Cécile and me) on site next week to re start the DAQ box

- Network installation

- Upgrade of CEPH disk array

- Installation (centos  $\rightarrow$  debian) of the Galileo machines to be used for AGATA GGP

- Topology Manager : modification to take into account the modifications for the GTS Tree

- Dut to Slow control moved from EPICS to IPbus

- Done

- To be installed and tested on site

- Grid machine GANAGATAGRID installed later on at LNL

- Upgrade of the script (gfal1 -> gfal2) tested on virtual machine

- Installation on ganagatagrid beginning of April

- Also the script to get back data from the grid has been upgraded by Jérémie D.

- ATRIUM link to doc here

- See file PlanDInstallation for more details

## Phase 2 developments :

- First version of a 'roadmap' document, on phase 2 electronic so far, released

See document ADP\_Part3

- Electronic Phase 2 integration

- Tests using STARE, ADF\_2\_STARE\_Emulator ongoing

- Modification of the UDP header packets (more suitable)

- Different network configurations tested up to Jumbo Frame

- Only with ADF\_2\_STARE\_Emulator

- Up to 7.5 Gb/s of transfer without losses for 2 UDP packets per ADF

- 10% losses for 1 ADF frame into one UDP packets

- Under investigations

- First in DCOD integration

- STAREEmulator → SQM → SQMReader → Pre-PSA → PSA

→ Consumer ADF

- Non definitive SQMReader so far (ada one inherited form another project)

- Some issues at the prePSA level ... uder inestigation

- Start discussions about the RUDP protocol implementation

## PSA and Tracking R&D (A. Boston)

Last Team meeting 7<sup>th</sup> March 2022.

Liverpool update:

- A009 scans data under analysis by Chris Everitt and Jack Hackett.

- C017 operational and under measurement coincidence scan to commence soon. Work led by Adem Kus.

- Fraser continuing working on the translation of the data to ADF format to allow easy distribution to the collaboration. Fraser has liaised with Jérémie and Olivier in this regard using compressed frames.

The new laboratory commissioning continues to be delayed due to issues with the security door and asbestos removal above the door. The new x-y positioning table and detector holding structure are entering final commissioning.

<u>Salamanca Update:</u> Salamanca have begun collecting some preliminary singles scan data from the A005 detector. The first scan was a 1 cm x 1 cm with an <sup>241</sup>Am source to get a view of the segments using a 3 mm collimator. A second scan is ongoing to get better info about the crystal position using a 1 mm collimator. They are expected to complete these initial scans by the end of March. They have experienced some issues with reliability (LN2, electronics). The plan for the 2D scan data collection was discussed in detail. The time required to collect the data should be short, the time required to verify the integrity of the data much longer.

<u>IPHC Update:</u> IPHC are investigating a crystal defect in the S001 prototype detector, multiple scans have been performed at a variety of bias voltages, a final scan will be performed at 2500V with the crystal slowly warmed to investigate temperature dependence. IPHC will be ready to receive A005 from April onwards. Building 25 (accelerator building) is supposed to be decontaminated from asbestos starting in July. This could hinder scans for several months. If A005 leaves Salamanca in June, it may be preferable to send it directly to GSI before to IPHC.

<u>GSI update:</u> The last germanium detector scan at GSI was 2 years ago, a double stripped planar detector. Crosstalk was observed between the X and Y strips. Presently they are a scanning particle detector, measuring Compton electrons. An upgrade of the position sensitive detector is planned. Use the present scanner (still 1mm resolution) to scan the new one prior replacement. Their intention is to remeasure the planar strip detector and then the A005 detector to compare with IPHC data. The GSI team are focused on the beam time for the DESPEC campaign which continues throughout June. After a break, the A005 scan could start from August onwards.

<u>Capsule availability</u> was discussed with HH. Due to constraints on the availability of A type capsules, the plan is to return A009 to IKP in the period before/after Easter. Details to be finalised.

Next Team meeting due mid-May.

## PSA

Last Team meeting 18<sup>th</sup> March 2022. Update received from Fraser.

In Liverpool the ML based High-Fold PSA development is progressing well, a graphaccelerated method to link Fold-1 solutions to higher-fold combinations shows promise however will likely need a significant re-write once a refined methodology is determined, preliminary results will hopefully be presented at the UK IOP NP conference in April with a second presentation at AGATA week detailing the complete methodology.

The work on self-calibration from York (has been observed to converge on noiseless test data (simulated), tests on simulated data with experimental noise were performed producing a reasonable observed deviation. (

Orsay is continuing with machine learning developments to accelerate PSCS. The experimental campaign at LNL is taking a lot of their focus at the moment, things should calm down at the end of April.

Next Team meeting due mid-May.

## Tracking

No significant items to report at this time.

#### **ORTEC** detector status update

The following update was received from ORTEC on 8th March

The AGATA program is finally starting to find some momentum. We received the longawaited flanges Monday 28/2/22. The assembly of the 7-pin feedthrough and other components is being completed these first couple of weeks in March. We are now able to queue the process on the AGATA detector. The program has progressed to the point I am now able to lay out the schedule for the process and test of the detector. It is as follows:

| AGA                      | TA Detector Program   |         |        |         |         |         |        |         |         |         |

|--------------------------|-----------------------|---------|--------|---------|---------|---------|--------|---------|---------|---------|

|                          |                       | March   |        |         |         |         | April  |         |         |         |

| Item                     | Task                  | Wk 2/28 | Wk 3/7 | Wk 3/14 | Wk 3/21 | Wk 3/28 | Wk 4/4 | Wk 4/11 | Wk 4/18 | Wk 4/25 |

| Flang                    | ge received           |         |        |         |         |         |        |         |         |         |

| Asse                     | mble                  |         |        |         |         |         |        |         |         |         |

|                          | Install 7-pin FTs     |         |        |         |         |         |        |         |         |         |

|                          | Clean flange          |         |        |         |         |         |        |         |         |         |

|                          | Contact board         |         |        |         |         |         |        |         |         |         |

|                          | Test pedestal         |         |        |         |         |         |        |         |         |         |

| Final                    | lize execution plan   |         |        |         |         |         |        |         |         |         |

|                          | Document installation |         |        |         |         |         |        |         |         |         |

|                          | Test plan             |         |        |         |         |         |        |         |         |         |

| Readiness of Fab Process |                       |         |        |         |         |         |        |         |         |         |

| Fabricate                |                       |         |        |         |         |         |        |         |         |         |

| Load                     |                       |         |        |         |         |         |        |         |         |         |

| Pump/Bake                |                       |         |        |         |         |         |        |         |         |         |

| Cool                     |                       |         |        |         |         |         |        |         |         |         |

| Leakage test             |                       |         |        |         |         |         |        |         |         |         |

| Resolution test          |                       |         |        |         |         |         |        |         |         |         |

The columns represent weeks. Those filled in with gray indicate work has begun or will begin. The blue blocks represent when completion is targeted. Ultimately, we will attempt to finalize testing of the AGATA detector and be prepared to host the factory visit the first week of May. The process on the AGATA detector element is complex and may have to be reworked. I have attempted to incorporate this eventuality in the above estimate.

#### Performance and Simulation (M. Labiche)

Source runs for AGATA:

As soon as detectors are mounted. March-April.

In-beam commissioning:

Three different in-beam commissioning experiments in preparation for the forthcoming AGATA physics campaign at Laboratori Nazionali di Legnaro. The aim will be to test and check the proper operational requirements of detectors, electronics, DAQ systems and analysis software. Reactions and setups have been chosen to simultaneously address different technical aspects and to optimize the beam time for this commissioning phase. Special attention will be given to complementary detectors, in agreement with the proposed experiments at the AGATA Pre-PAC Workshop.

The commissioning experiments will be organized as follows:

Phase 1: AGATA+PRISMA: part of the time dedicated to the actual test of operation of AGATA and AGATA-PRISMA coincidences in real in-beam conditions. Part of the time to test new PRISMA electronics. DANTE array will be also added and tested.

Phase 2: AGATA+SPIDER dedicated to the in-beam test of this particular setup for which we expect to have a number of proposal (based on the LoI presented at the Legnaro workshop).

Phase 3: test of the AGATA+ REVERSE PLUNGER SETUP dedicated to the in-beam test of this particular setup for which we expect to have a number of proposal (based on the LoI presented at the Legnaro workshop).

Phase 1 and 2 before the beginning of the physics campaign and Phase 3 by the end of July 2022.

#### Simulations:

Next WG meeting is expected within the next couple of weeks and will focus on Topical Issue for AGATA.

#### Code development:

user-commands have been defined to rotate SPIDER, independently of AGATA. SPIDER geometry was imported from CAD and converted into gdml. Up to now, AGATA needed to be rotated to have SPIDER at the right position. This resulted in a clash between the AGATA array and the new reaction chamber, also imported from CAD.

New user-command takes 3 parameters: the angle with respect to x, y and z axis, in degrees. In the example below, we are rotating SPIDER only w/r to the y axes by 65 degrees.

**Dissemination (J. Nyberg)**

#### AGATA Week : - Program to be done Urgently !!